ADSP-21368 SHARC Processor Hardware Reference A-131

Register Reference

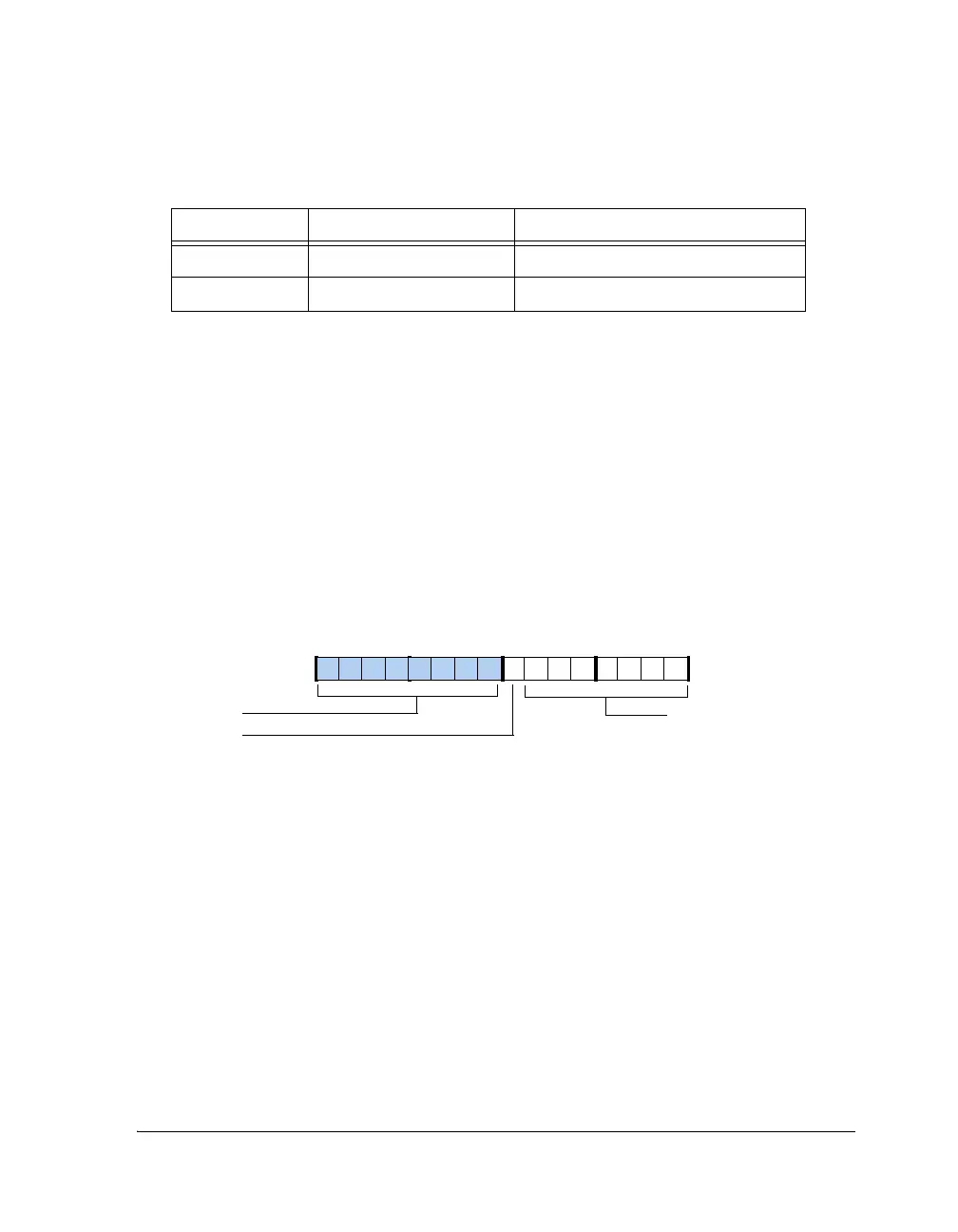

Master Internal Time Register (TWIMITR)

The TWI control register (TWIMITR, shown in Figure A-57 and described

in Table A-54) is used to enable the TWI module as well as to establish a

relationship between the peripheral clock (PCLK) and the TWI controller’s

internally-timed events. The internal time reference is derived from PCLK

using the prescaled value:

PRESCALE = f

PCLK

/10 MHz

0x4488 RXTWI8 8-Bit FIFO Receive Register

0x448C RXTWI16 16-Bit FIFO Receive Register

Figure A-57. Master Internal Time Register

Table A-53. TWI Register Descriptions (Cont’d)

Address Name Description

TWIMITR (0x4404)

PRESCALE

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

Reserved

TWIEN

Prescale

The number of peripheral

clock (PCLK) periods used in

the generation of one internal

time reference.

TWI Enable

0=Disable TWI

1=Enable TWI master and slave mode operation

Loading...

Loading...