ADSP-21368 SHARC Processor Hardware Reference A-71

Register Reference

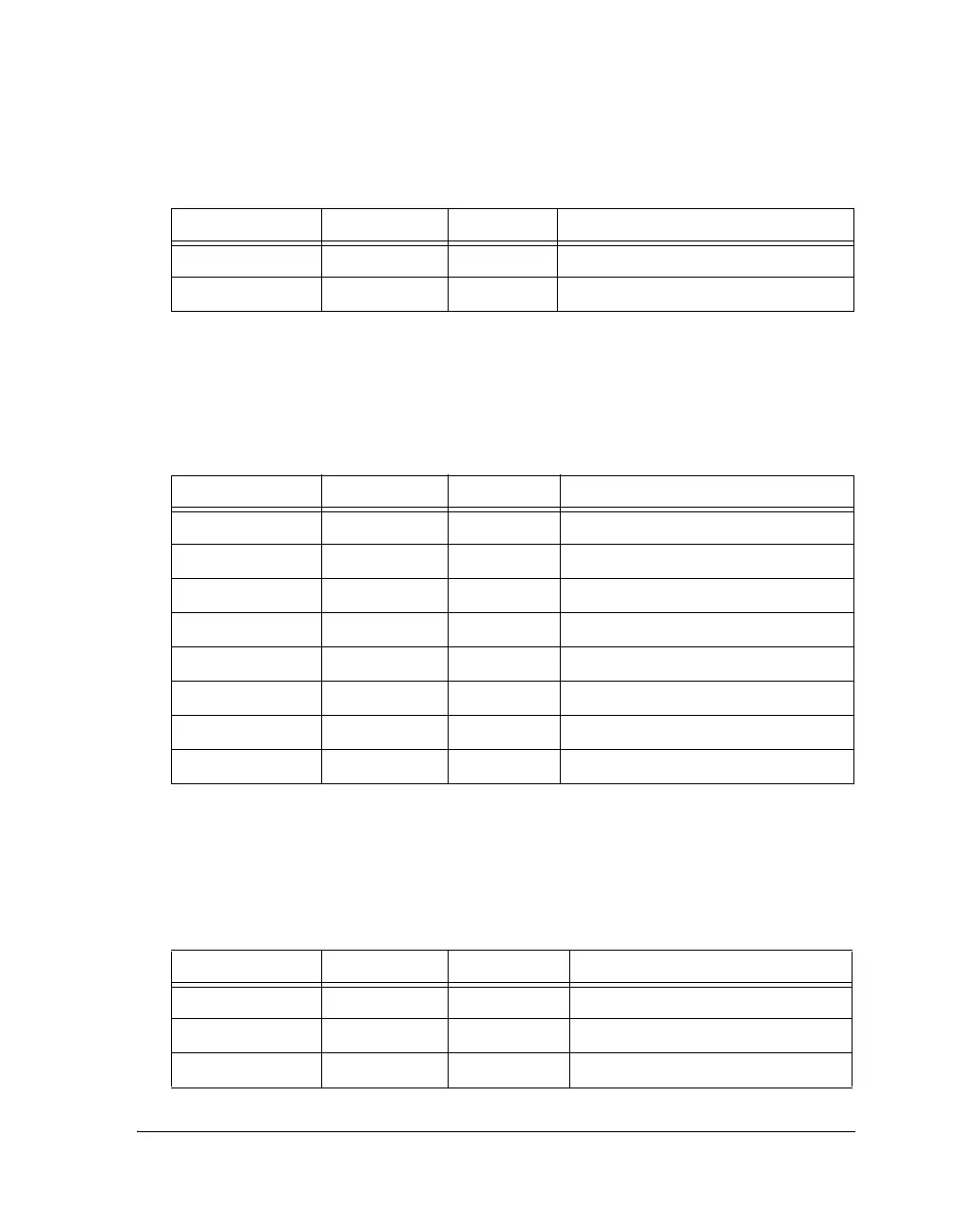

IDP_DMA_Mx

Table A-20 provides information about the IDP DMA modifier registers.

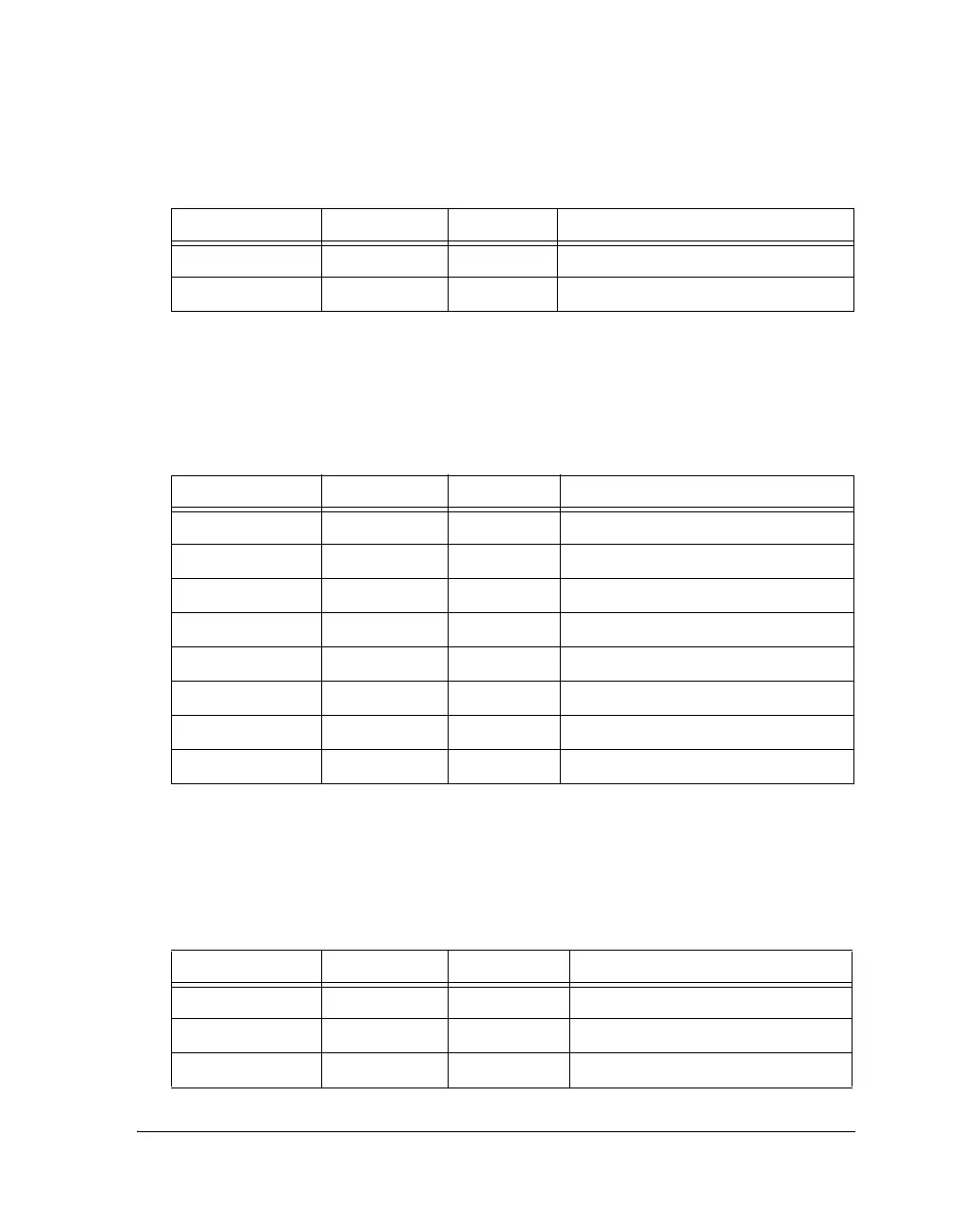

IDP_DMA_Cx

Table A-21 provides information about the IDP DMA counter registers.

IDP_DMA_I6 0x2406 0x00000 IDP channel 6 DMA index register

IDP_DMA_I7 0x2407 0x00000 IDP channel 7 DMA index register

Table A-20. IDP_DMA_Mx Registers

Register Address Reset State Description

IDP_DMA_M0 0x2410 0x00 IDP channel 0 DMA modifier register

IDP_DMA_M1 0x2411 0x00 IDP channel 1 DMA modifier register

IDP_DMA_M2 0x2412 0x00 IDP channel 2 DMA modifier register

IDP_DMA_M3 0x2413 0x00 IDP channel 3 DMA modifier register

IDP_DMA_M4 0x2414 0x00 IDP channel 4 DMA modifier register

IDP_DMA_M5 0x2415 0x00 IDP channel 5 DMA modifier register

IDP_DMA_M6 0x2416 0x00 IDP channel 6 DMA modifier register

IDP_DMA_M7 0x2417 0x00 IDP channel 7 DMA modifier register

Table A-21. IDP_DMA_Cx Registers

Register Address Reset State Description

IDP_DMA_C0 0x2420 0x00000 IDP channel 0 DMA count register

IDP_DMA_C1 0x2421 0x00000 IDP channel 1 DMA count register

IDP_DMA_C2 0x2422 0x00000 IDP channel 2 DMA count register

Table A-19. IDP_DMA_Ix Registers (Cont’d)

Register Address Reset State Description

Loading...

Loading...