Parallel Data Acquisition Port (PDAP)

7-10 ADSP-21368 SHARC Processor Hardware Reference

This mode sends one 32-bit word to FIFO for each input clock cycle—the

DMA transfer rate matches the PDAP input clock rate.

Packing Mode 10

On the first clock edge (cycle A), the packing unit latches parallel data up

to 16 bits wide (bits 19–4 of the parallel input) and places it in bits 15–0

(the lower half of the word), then waits for the second clock edge (cycle

B). On the second clock edge (cycle B), the packing unit takes the same

set of inputs and places the word into bits 31–16 (the upper half of the

word).

This mode sends one packed 32-bit word to FIFO for every two input

clock cycles—the DMA transfer rate is one-half the PDAP input clock

rate.

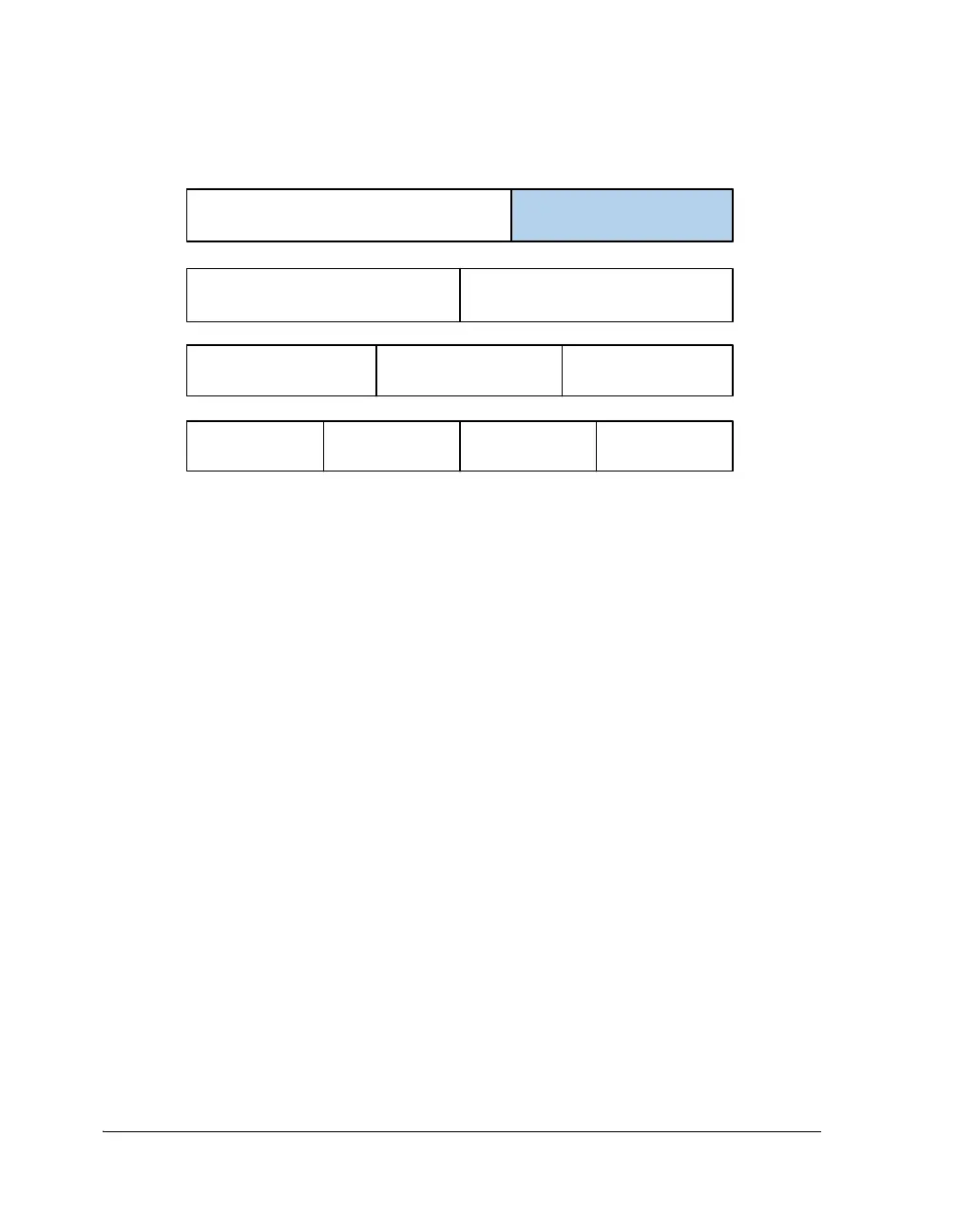

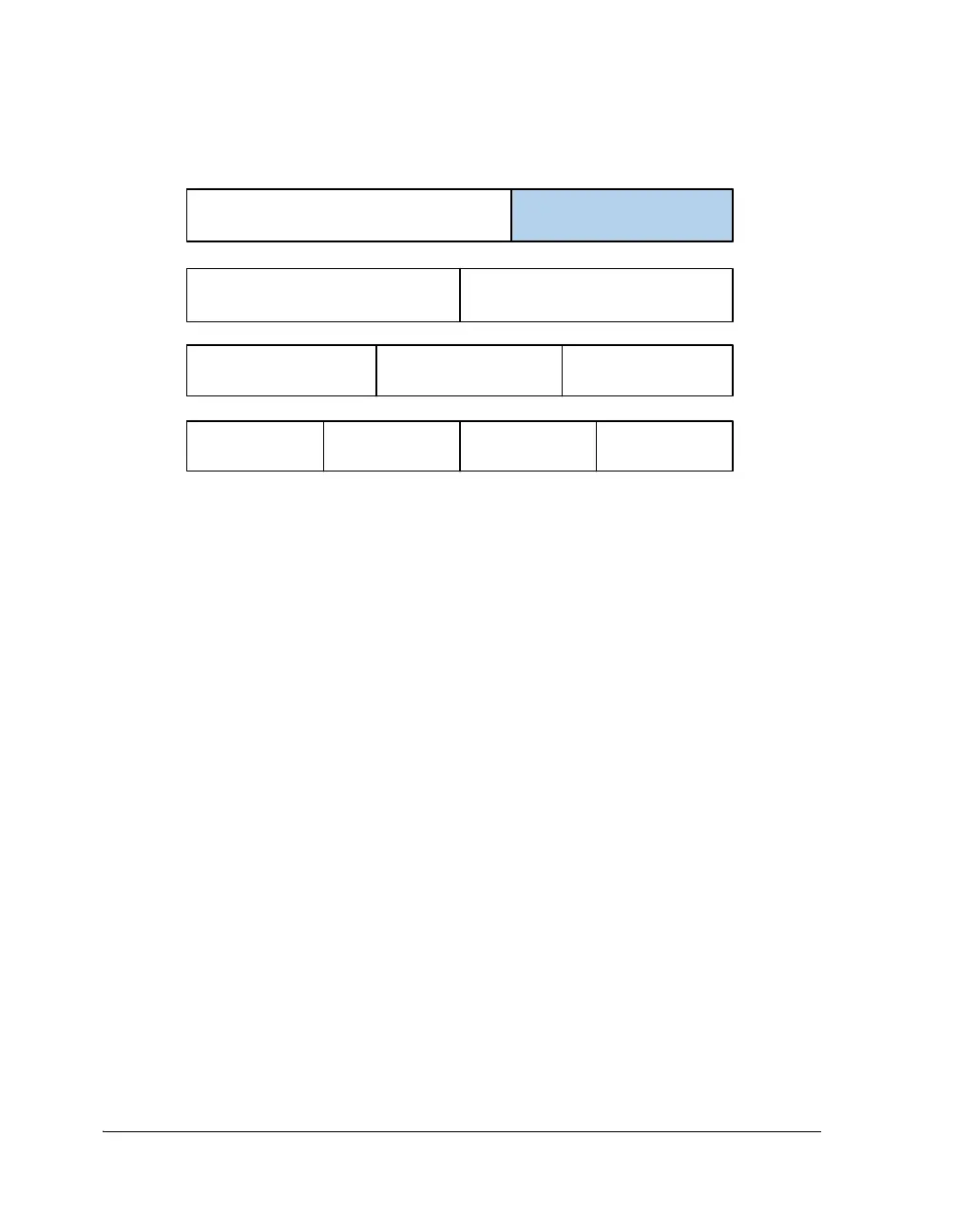

Figure 7-13. Packing Modes in PDAP

31 24 23 16 15 7 0

31 21 20 10 9 0

31 16 15 0

MODE 10

2x16-bit

MODE 01

tri-word

MODE 00

4x8-bit

B A

ABC

ABCD

MODE 11

1x20-bit

31 12 11 0

A RESERVED

8

Loading...

Loading...