ADSP-21368 SHARC Processor Hardware Reference 14-47

System Design

The initial boot of the 256-word loader kernel requires an 8-bit host to

transmit 1536 8-bit words. The SPI DMA count value of 0x180 is equal

to 384 words. Since one 32-bit word is created from four packed 8-bit

words, the total number of 8-bit words transmitted is 1536.

For all boot modes, the VisualDSP++ loader automatically outputs the

correct word width and count based on the project settings. For more

information, see the VisualDSP++ tools documentation.

Slave Boot Mode

In slave boot mode, the host processor initiates the booting operation by

activating the

SPICLK signal and asserting the SPIDS signal to the active

low state. The 256-word kernel is loaded 32 bits at a time, through the

SPI receive shift register (RXSR). To receive 256 instructions (48-bit

words) properly, the SPI DMA initially loads a DMA count of 0x180

(384) 32-bit words, which is equivalent to 0x100 (256) 48-bit words.

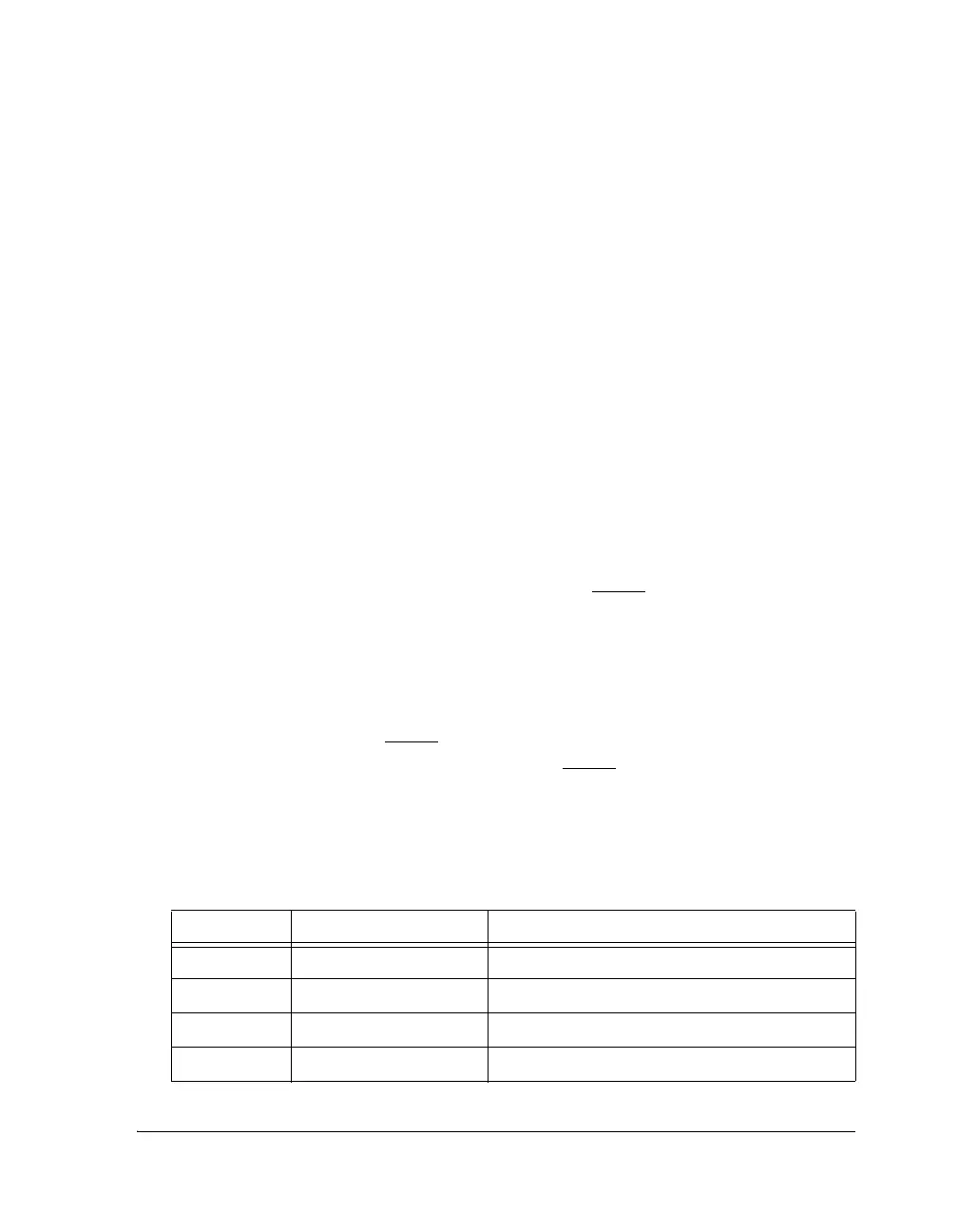

L

The processor’s SPIDS pin should not be tied low. When in SPI

slave mode, including booting, the SPIDS signal is required to tran-

sition from high to low. SPI slave booting uses the default bit

settings shown in Table 14-11.

SPI word 9 = 0xBB

SPI word 10 = 0xAA

SPI word 11 = 0x88

SPI word 12 = 0x77

Table 14-11. SPI Slave Boot Bit Settings

Bit Setting Comment

SPIEN Set (= 1) SPI enabled

SPIMS Cleared (= 0) Slave device

MSBF Cleared (= 0) LSB first

WL 10, 32-bit SPI Receive shift register word length

Loading...

Loading...