Serial Peripheral Interface DMA

2-42 ADSP-21368 SHARC Processor Hardware Reference

Chain insertion mode operates the same as non-chained DMA mode.

When the current DMA transfer ends, an interrupt request occurs and no

TCBs are loaded. This interrupt request is independent of the

PCI bit

state.

Chain insertion should not be set up as an initial mode of operation. This

mode should only be used to insert one or more TCBs into an active

DMA chaining sequence.

Serial Peripheral Interface DMA

The serial peripheral interface supports both standard and chained DMA.

However, unlike the serial ports, programs cannot insert a TCB in an

active chain using the SPI.

Setting Up and Starting Chained DMA over the SPI

Configuring and starting chained DMA transfers over the SPI port is the

same as for the serial port, with one exception. Contrary to SPORT DMA

chaining, (where the first DMA in the chain is configured by the first

TCB), for SPI DMA chaining, the first DMA is not initialized by a TCB.

Instead, the first DMA in the chain must be loaded into the SPI parameter

registers (IISPI, IMSPI, CSPI), and the chain pointer register (CPSPI)

points to a TCB that describes the second DMA in the sequence.

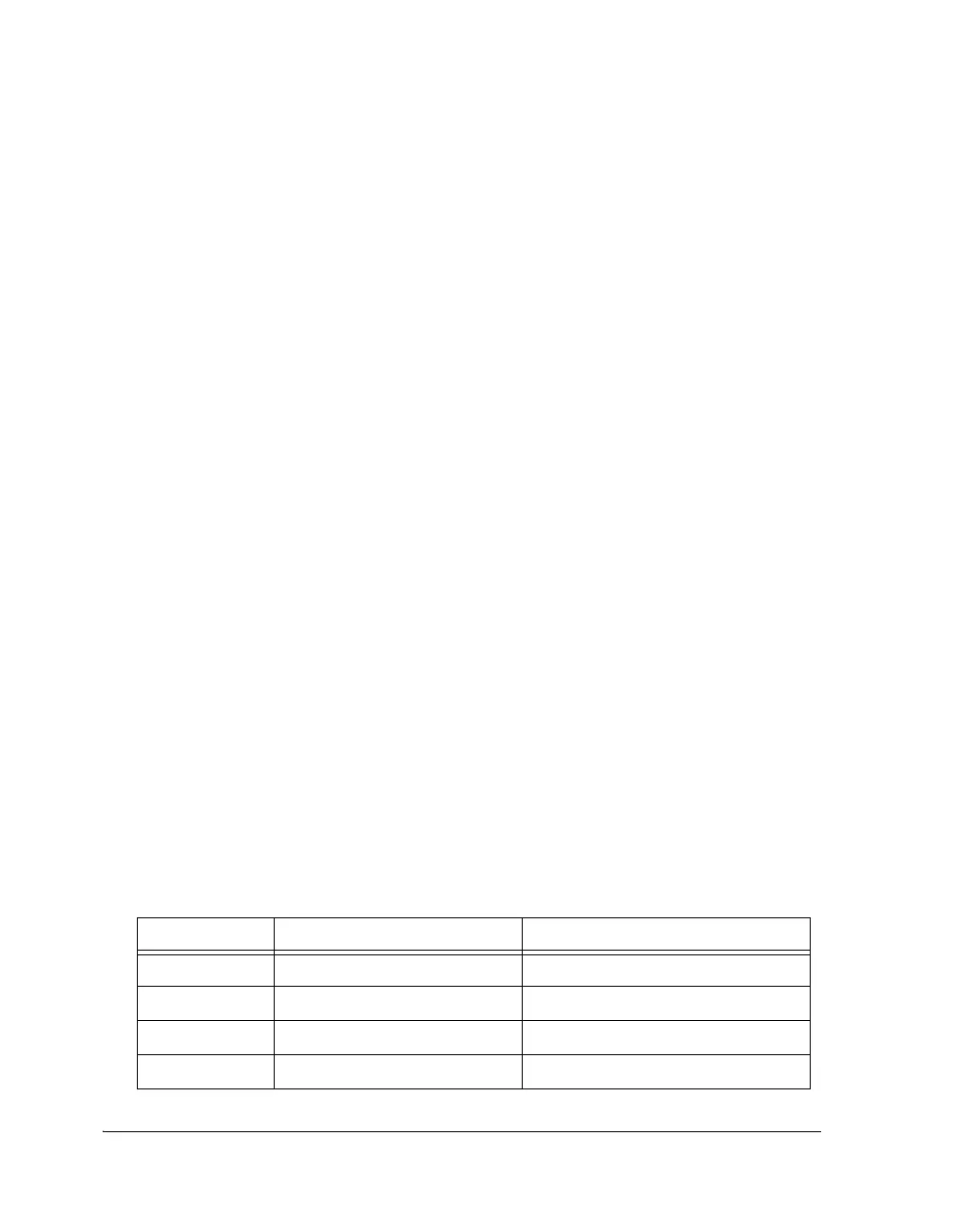

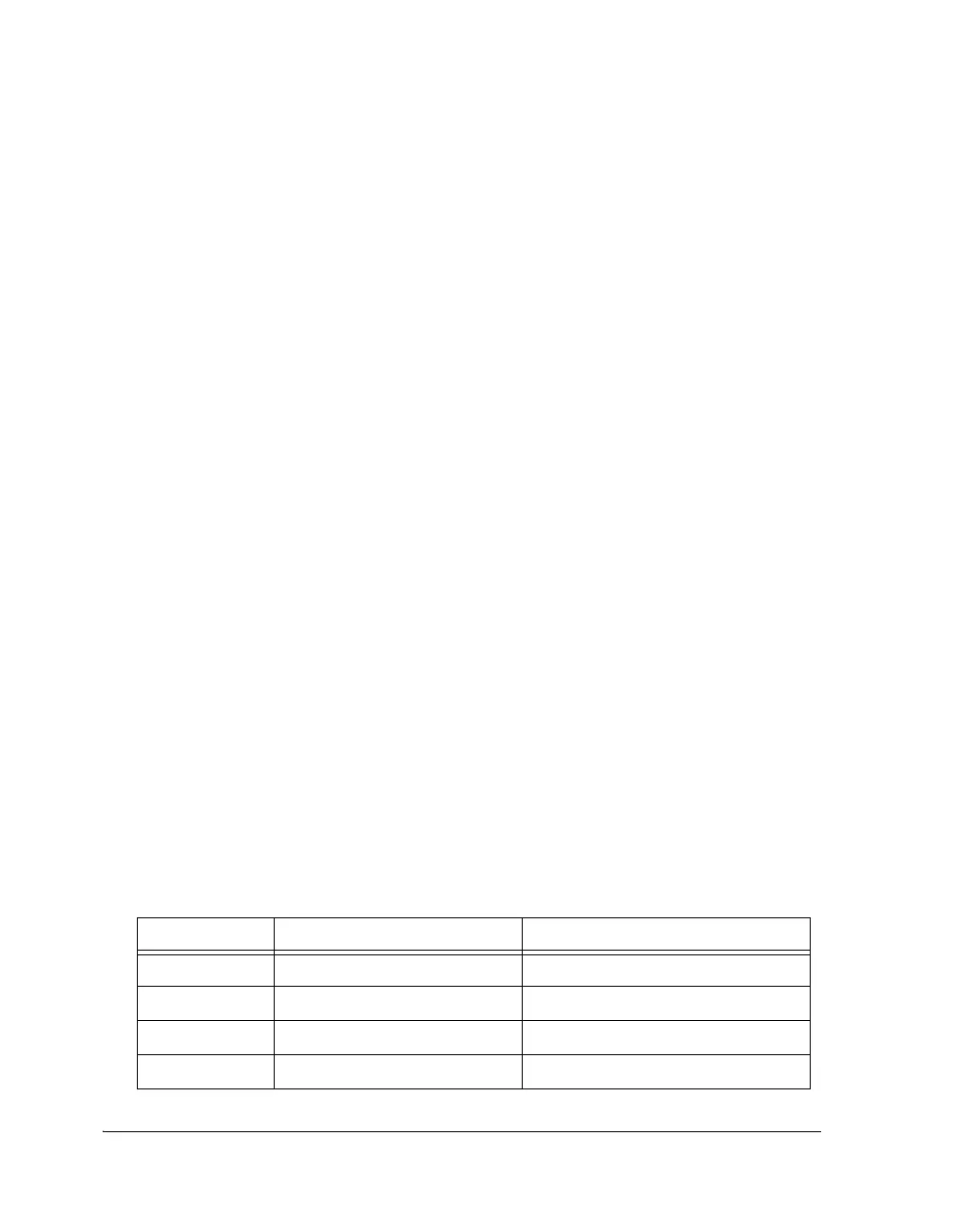

Table 2-12 shows the order of register loading.

Table 2-12. DMA Chaining Sequence

Address Register Description

CPSPI DMA Start Address Address in memory

CPSPI – 1 DMA Address Modifier Address increment

CPSPI – 2 DMA Word Count Number of words to transfer

CPSPI – 3 DMA Next TCB Pointer to address of next TCB

Loading...

Loading...