Architectural Overview

1-6 ADSP-21368 SHARC Processor Hardware Reference

Architectural Overview

The ADSP-21367/8/9 and ADSP-2137x processors form a complete sys-

tem-on-a-chip, integrating a large, high speed SRAM and I/O peripherals

supported by a dedicated I/O bus. The following sections summarize the

features of each functional block in the processor architecture, which

appears in Figure 1-1.

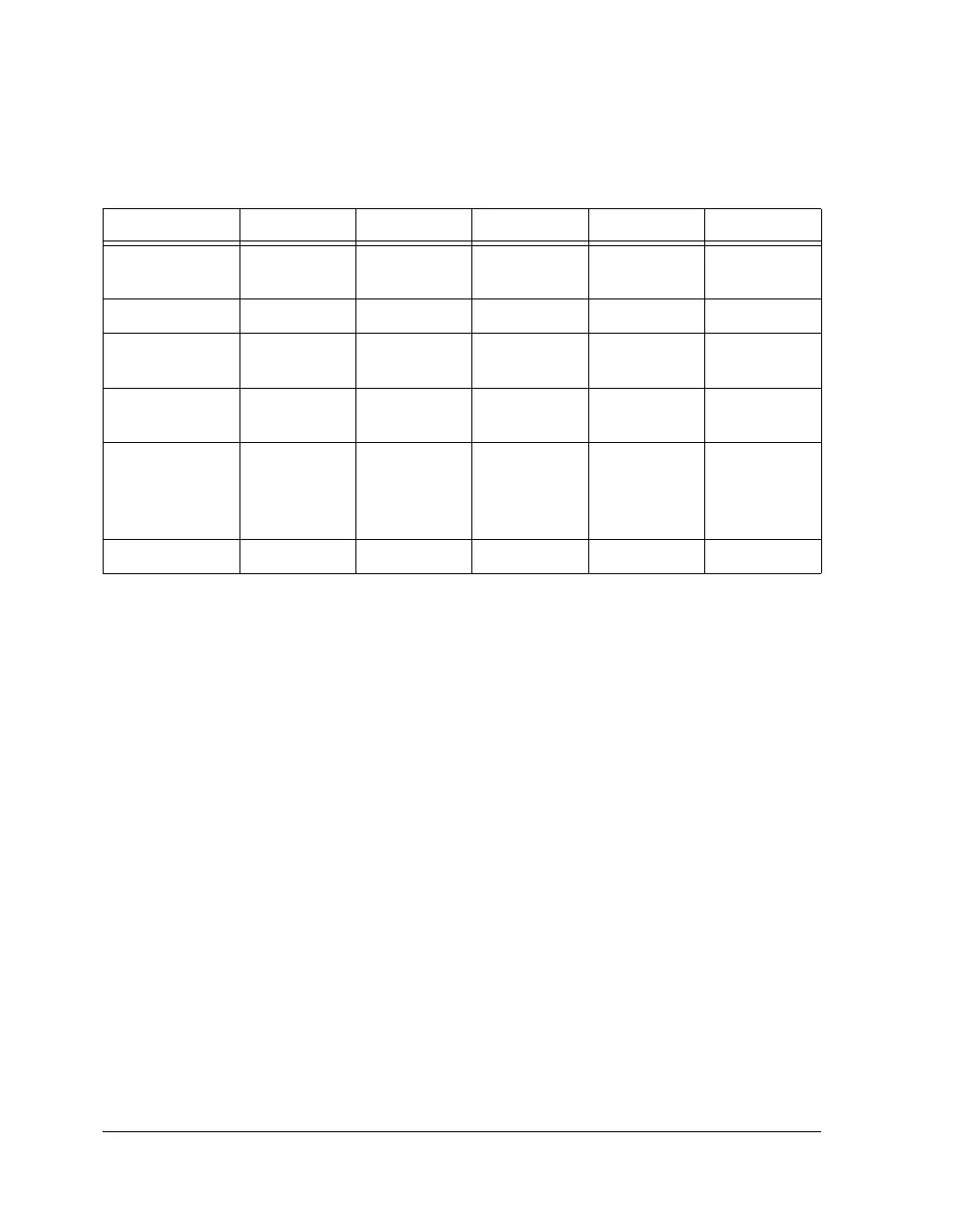

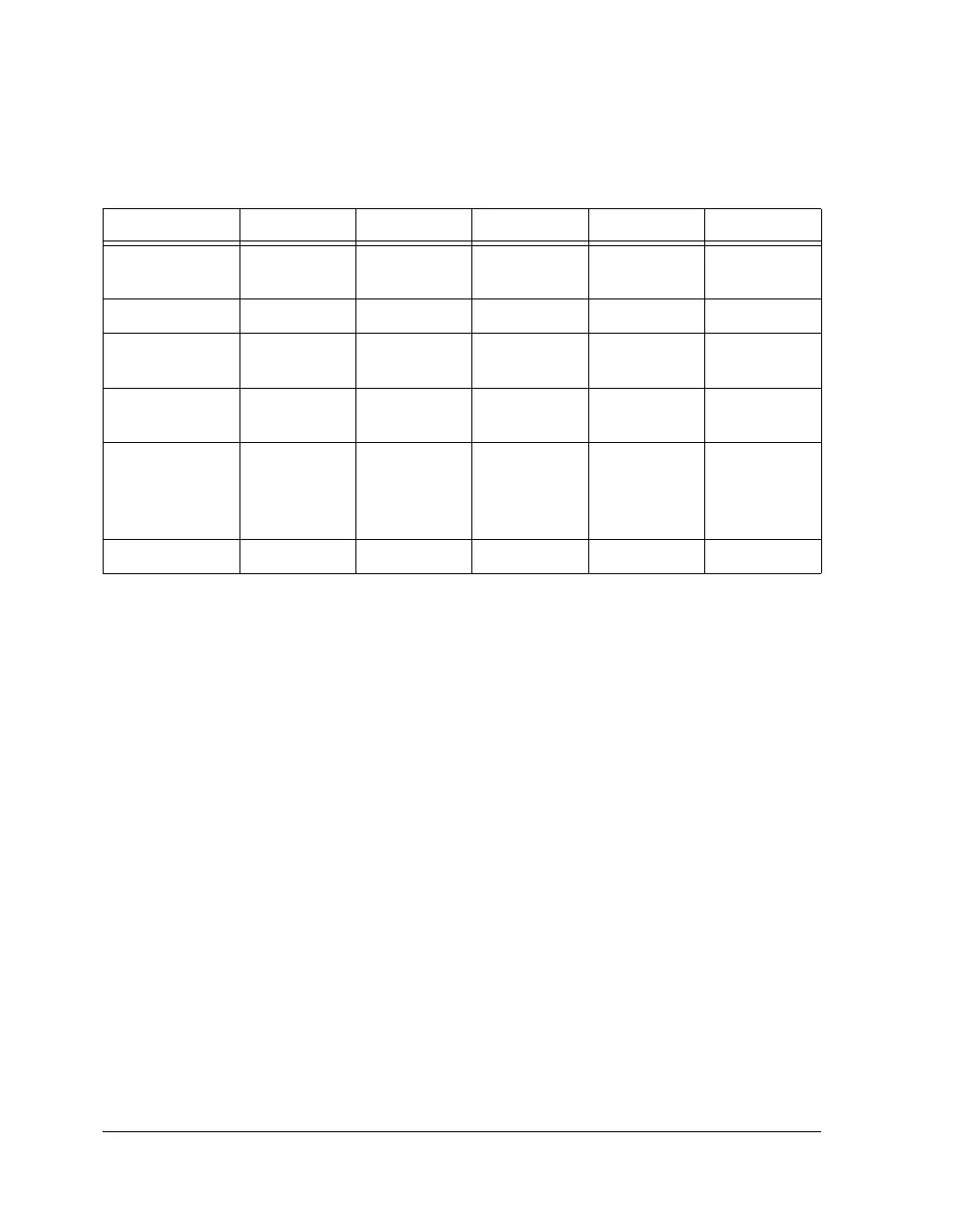

Pulse Width

Modulation

Yes Yes Yes Yes No

S/PDIF Yes Yes Yes Yes No

Shared

Memory

NoYesNoNoNo

SRC

Performance

128dB 140dB 128dB 128dB N/A

Package Option

3

256-ball

SBGA

208 Lead

MQFP

256-ball

SBGA

256-ball

SBGA

208 Lead

MQFP

208-lead

MQFP

208-lead

MQFP

Processor Speed 333 MHz 333 MHz 333 MHz 266 MHz 266 MHz

1 The ADSP-21367 processor include a customer-definable ROM block. Please contact your Analog

Devices sales representative for additional details.

2 Audio decoding algorithms include PCM, Dolby Digital EX, PCM, Dolby Digital EX, Dolby Pro-

logic IIx, DTS 96/24, Neo:6, DTS ES, MPEG2 AAC, MPEG2 2channel, MP3, and functions like

bass management, delay, speaker equalization, graphic equalization, and more. Decoder/post-proces-

sor algorithm combination support will vary depending upon the chip version and the system config-

urations. Please visit www.analog.com/SHARC for complete information.

3 Analog Devices offers these packages in lead-free (Pb) versions.

Table 1-1. SHARC Processor Features (Cont’d)

Feature ADSP-21367 ADSP-21368 ADSP-21369 ADSP-21371 ADSP-21375

Loading...

Loading...