ADSP-21368 SHARC Processor Hardware Reference 1-3

Introduction

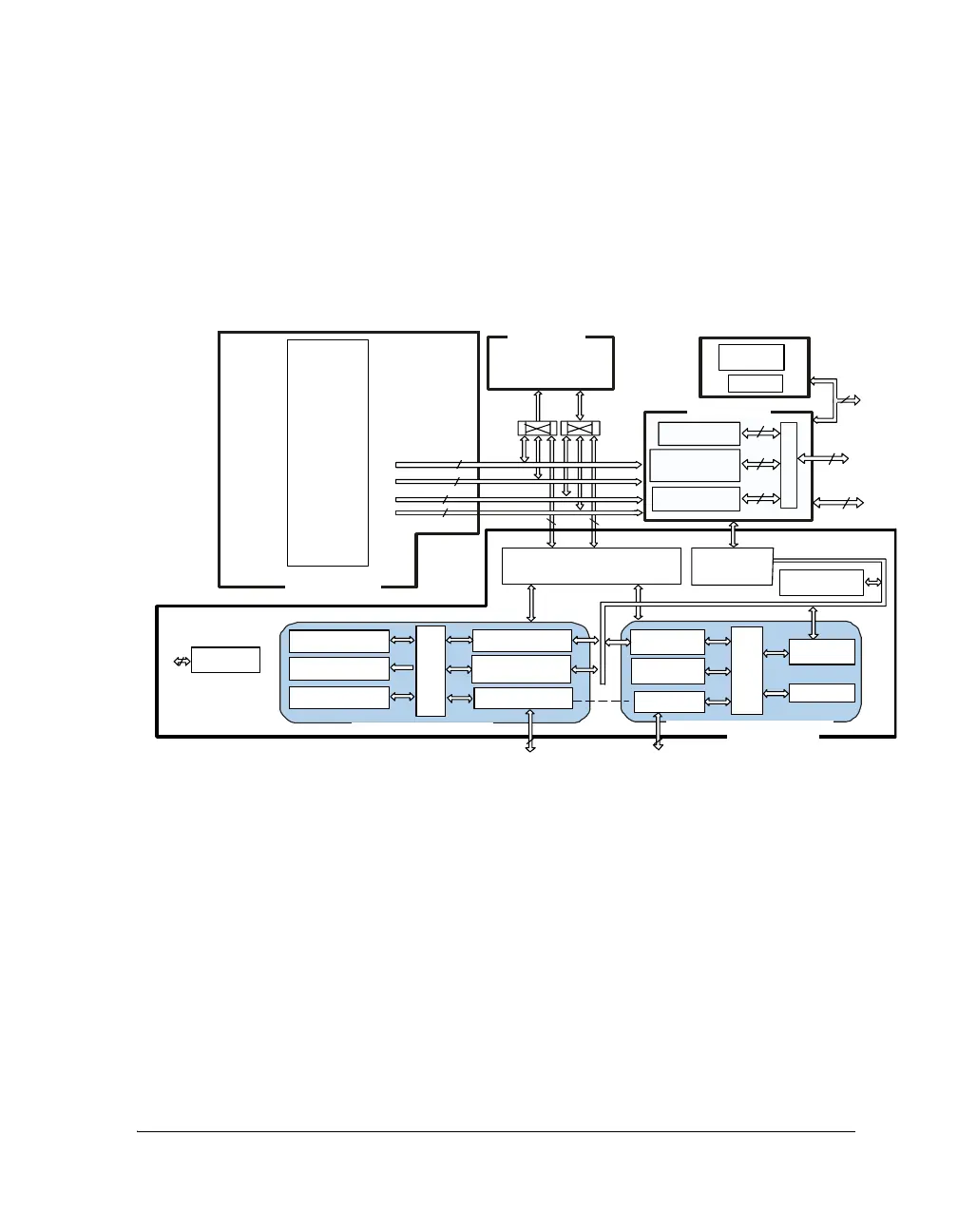

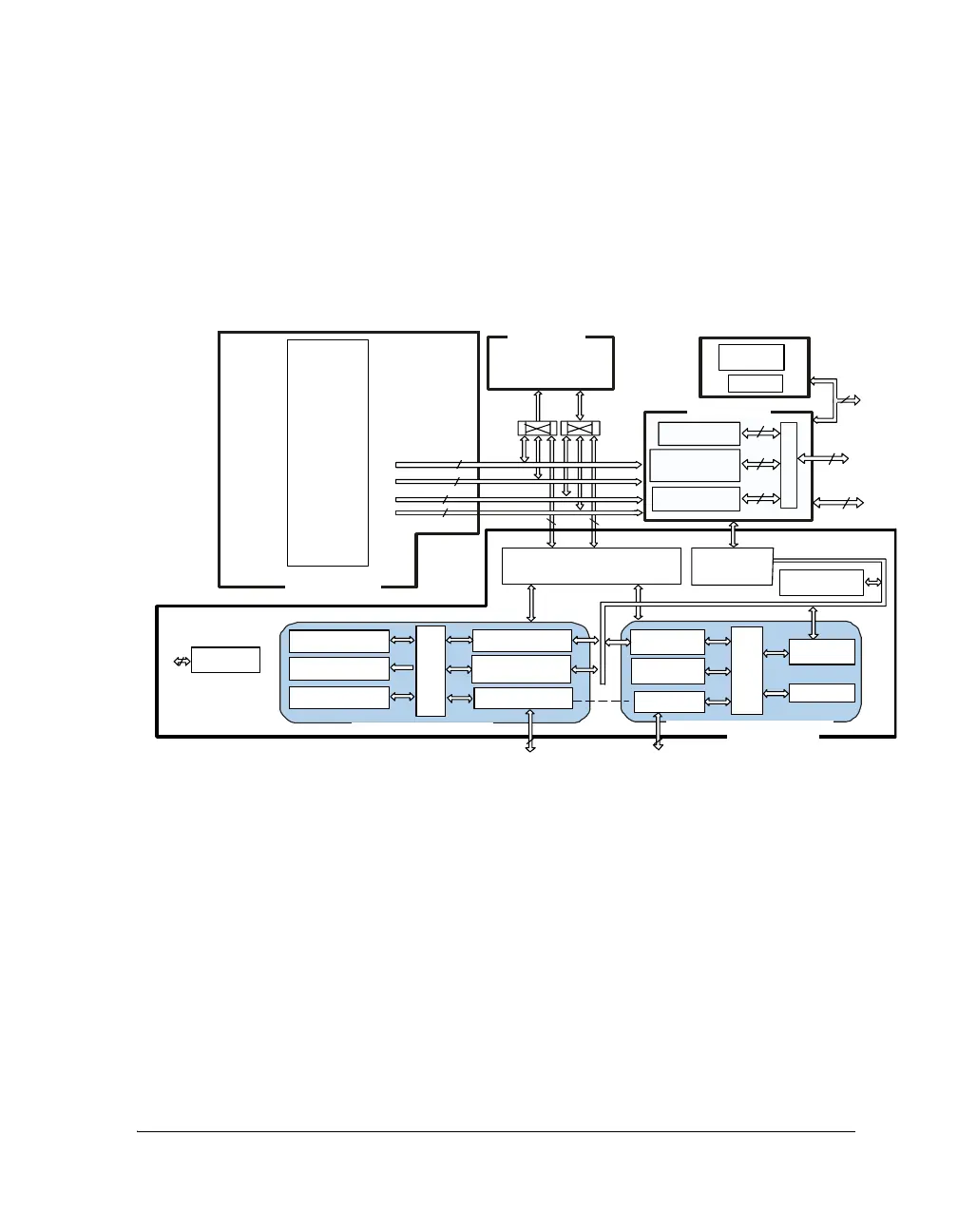

from memory, access an instruction (from the cache), and perform a

DMA transfer.

Figure 1-1 also shows the asychronous memory interface available on the

ADSP-21368 processor.

The ADSP-21367/8/9 and ADSP-2137x processors address the five cen-

tral requirements for signal processing:

Fast, Flexible Arithmetic. The ADSP-21000 family processors execute all

instructions in a single cycle. They provide fast cycle times and a complete

set of arithmetic operations. The processor is IEEE floating-point compat-

ible and allows either interrupt on arithmetic exception or latched status

exception handling.

Figure 1-1. ADSP-21368 Block Diagram

SPI PO RT (2 )

TIMERS (3)

TWO WIRE

INTERFACE

UART (2)

DPI ROUTING UNIT

DIGITAL PERIPHERAL INTERFACE

GPIO FLAGS/

IRQ/ TI ME XP

4

SERIAL PORTS(8)

INPUT DATA PORT/

PDAP

DAI ROUTING UNIT

SPDIF (RX/TX)

DIGITAL AUDIO INTERFACE

IOD(32)

ADD R DA TA

IOA(24)

ON-CHIP MEMORY

PM DATA BUS

DM DATABUS

32PM ADDRESS BUS

DM ADDRESS BUS

64

PX REGIS TER

2PROCESSING

ELEMENTS

(PEX, PEY)

PROGRAM

SEQ UENCER

TIMER

INSTRUCTION

CACHE

32X 48-BIT

CORE PROCESSOR

DMA

CONTROLLER

34 CHANNELS

S

ME MORY -TO-

ME MORY D MA (2)

IOP REG ISTER (MEMORY MAPPED)

CONTROL, STATUS, & DATA BUFFERS

2DAGS

8X4X32

I/O PROCESSOR

DAI PINS

DP I PI NS

64

32

14

20

SRC (8 CHANNELS)

PRECISION CLOCK

GENERATORS (4)

*THE ADSP-21368 PROCESSOR INCLUDES A CUSTOMER-DEFINABLE ROM BLOCK.

PLEAS E CONTACT YOUR ANALOG DE VICES SALES REPRES ENTATIVE FO R ADDITIO NAL DETAILS

24

18

SDRAM

CONTROLLER

ADDRESS

CONTROL

3

8

AS YN C HRONO US

MEMORY

INTERFACE

SHARED MEMORY

INTERFACE

8

EXTERNAL PORT

C

O

N

T

R

O

L

P

I

N

S

PWM

32

DATA

FLAGS

4-15

Loading...

Loading...