ADSP-21368 SHARC Processor Hardware Reference A-9

Register Reference

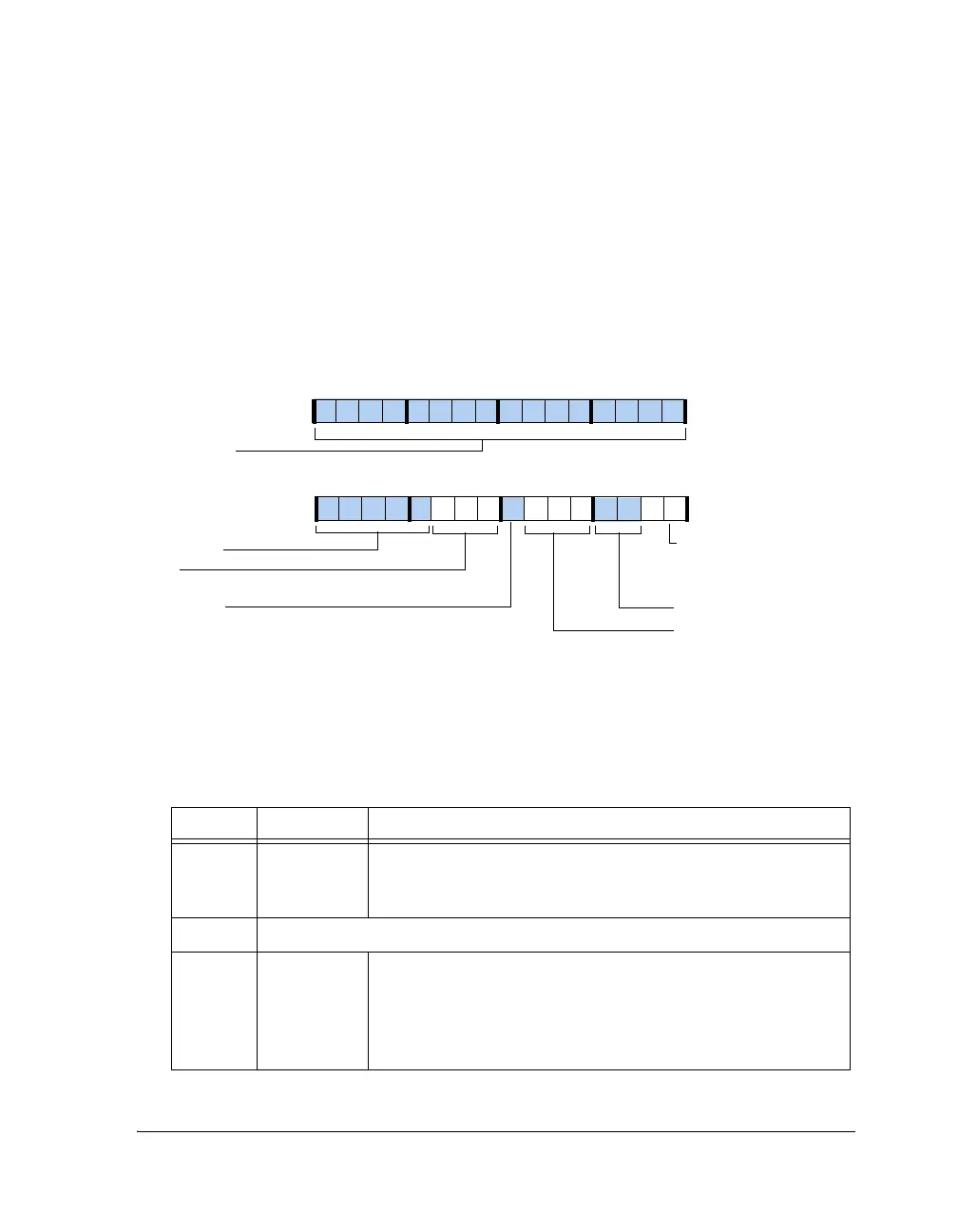

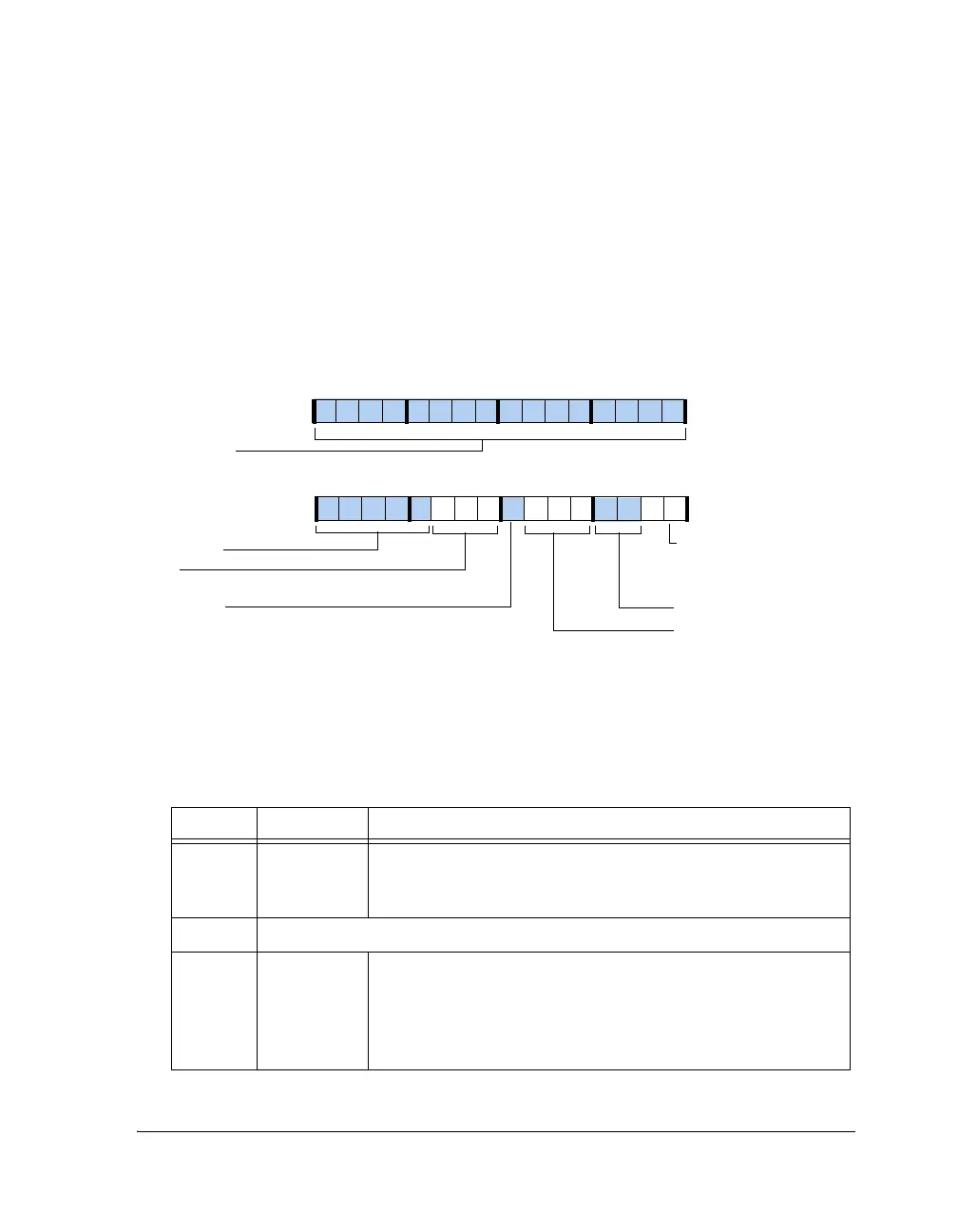

System Status Register (SYSTAT)

The SYSTAT register’s address is 0x180F. The reset value has all bits initial-

ized to zero, except for the IDC, CRBM, and CRAT fields, which are set from

values on the ADSP-21367/8/9 and ADSP-2137x’s pins. This register is

shown in Figure A-3 and described in Table A-2.

Table A-2. System Status Register (SYSTAT) Bit Descriptions

Bit Name Description

0BSYNBus Synchronized. Indicates whether the processor’s bus arbitration

logic is synchronized (if set, =1) or is not synchronized (if cleared,

=0, reset value).

3–1 Reserved (reset value =0)

6-4 CRBM Current Bus Master. These bits indicate the ID of the processor

that currently is the bus master in a multiprocessor system. Because

CRBM is only valid for DSPs with ID inputs other than zero (for

example, a multiprocessor system), the processor keeps CRBM set

to 001 when ID equals 000. The reset value of CRBM is undefined.

Figure A-3. SYSTAT Register

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

BSYN

IDC

CRBM

Current Bus Master

Status of ID of processor that is

current bus master

Bus Synchronized

1=Bus arbitration synchronized

0=Not synchronized

SYSTAT(0x180F)

31 30 29 28 27 26 24 23 22 21 20 19 18 17 16

0000000000000000

Reserved

25

0000000000000000

ID Code. State of ID2–0 pins

Reserved

Reserved

Reserved

Loading...

Loading...