Two Wire Interface Registers

A-130 ADSP-21368 SHARC Processor Hardware Reference

L

Apart from the DMA control and status registers there are index,

modifier, count, and chain pointer registers for both the transmit

and receive DMA channels. For more information on these regis-

ters, see “Port, Buffer, and DMA Control Registers” on page 2-26,

and Table 2-13, “UART DMA Registers,” on page 2-44.

Two Wire Interface Registers

The two wire interface (TWI) registers (described in Table A-53) provide

all control and status bits for this peripheral. Status bits can be updated by

their respective functional blocks.

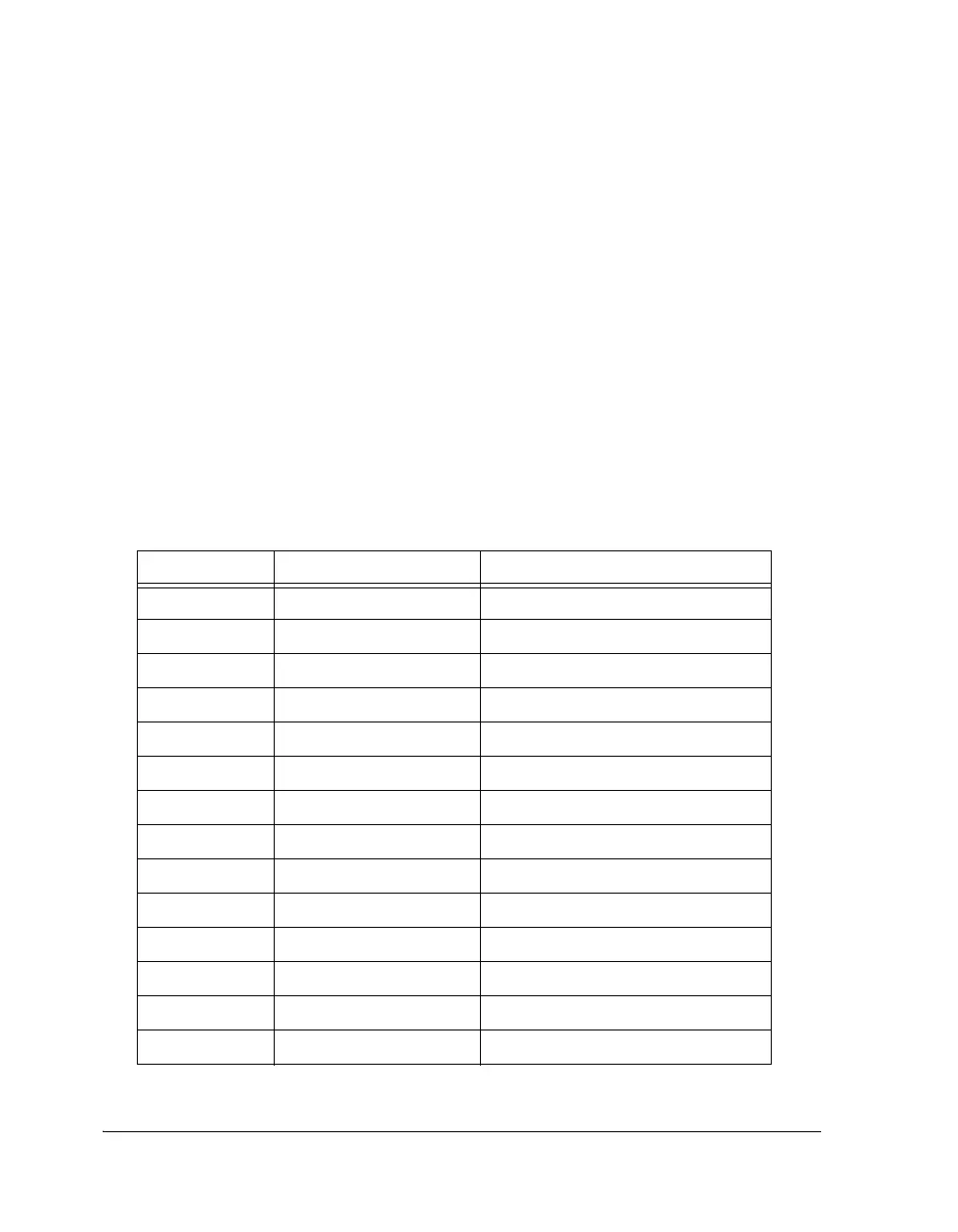

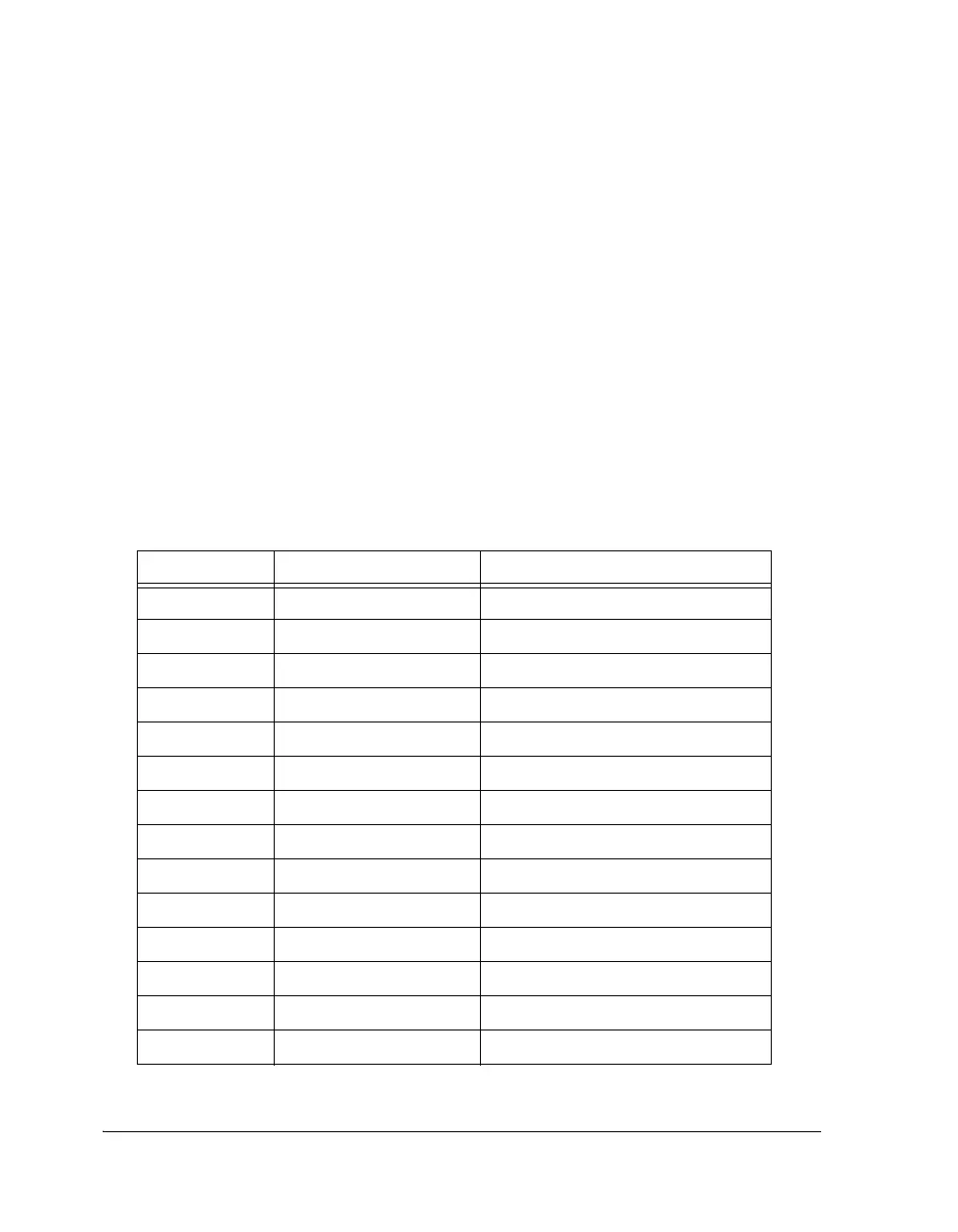

Table A-53. TWI Register Descriptions

Address Name Description

0x4400 TWIDIV SCL Clock Divider

0x4404 TWIMITR Master Internal Time Reference

0x4408 TWISCTL Slave Mode Control

0x440C TWISSTAT Slave Mode Status

0x4410 TWISADDR Slave Mode Address

0x4414 TWIMCTL Master Mode Control

0x4418 TWIMSTAT Master Mode Status

0x441C TWIMADDR Master Mode Address

0x4420 TWIIRPTL Interrupt Latch

0x4424 TWIIMASK Interrupt Mask

0x4428 TWIFIFOCTL FIFO Control

0x442C TWIFIFOSTAT FIFO Status

0x4480 TXTWI 8 8-bit FIFO Transmit Register

0x4484 TXTWI 16 16-bit FIFO Transmit Register

Loading...

Loading...