ADSP-21368 SHARC Processor Hardware Reference A-85

Register Reference

PWM Dead Time Registers (PWMDTx)

These registers, described in Table A-32, set up a short time delay between

turning off one PWM signal and turning on its complementary signal.

These 10-bit, read/write registers are located at addresses:

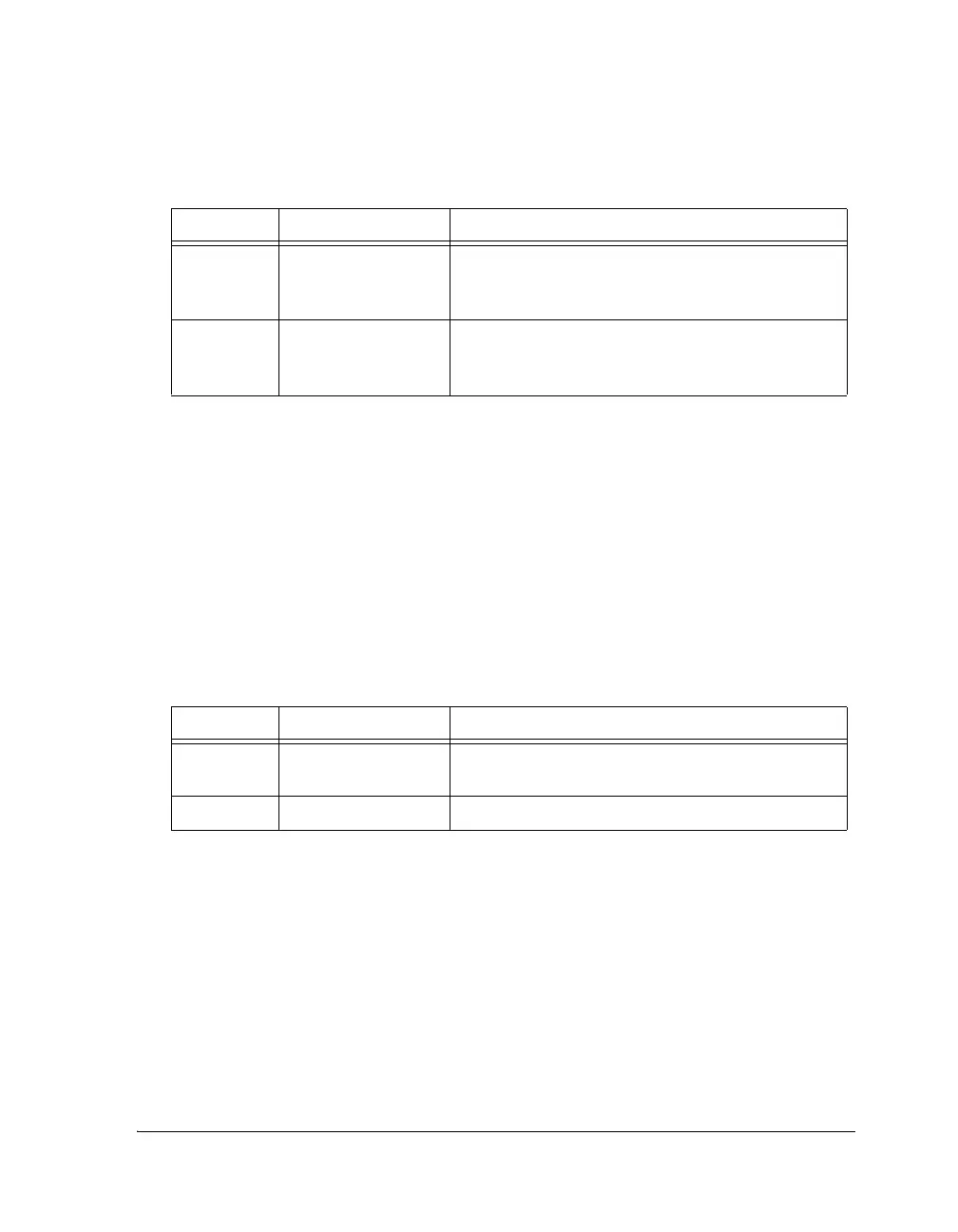

Table A-31. PWMALx/PWMBLx Register Bit Descriptions

Bit Name Description

15–0 PWMALx Channel AL Duty Cycle. Program a two’s complement

duty cycle with a value of 0x0000 through 0xFFFF.

Default = 0

15–0 PWMBLx Channel BL Duty Cycle. Program a two’s complement

duty cycle with a value of 0x0000 through 0xFFFF.

Default = 0

PWMDT0—0x3003 PWMDT2—0x3403

PWMDT1—0x0013 PWMDT3—0x3413

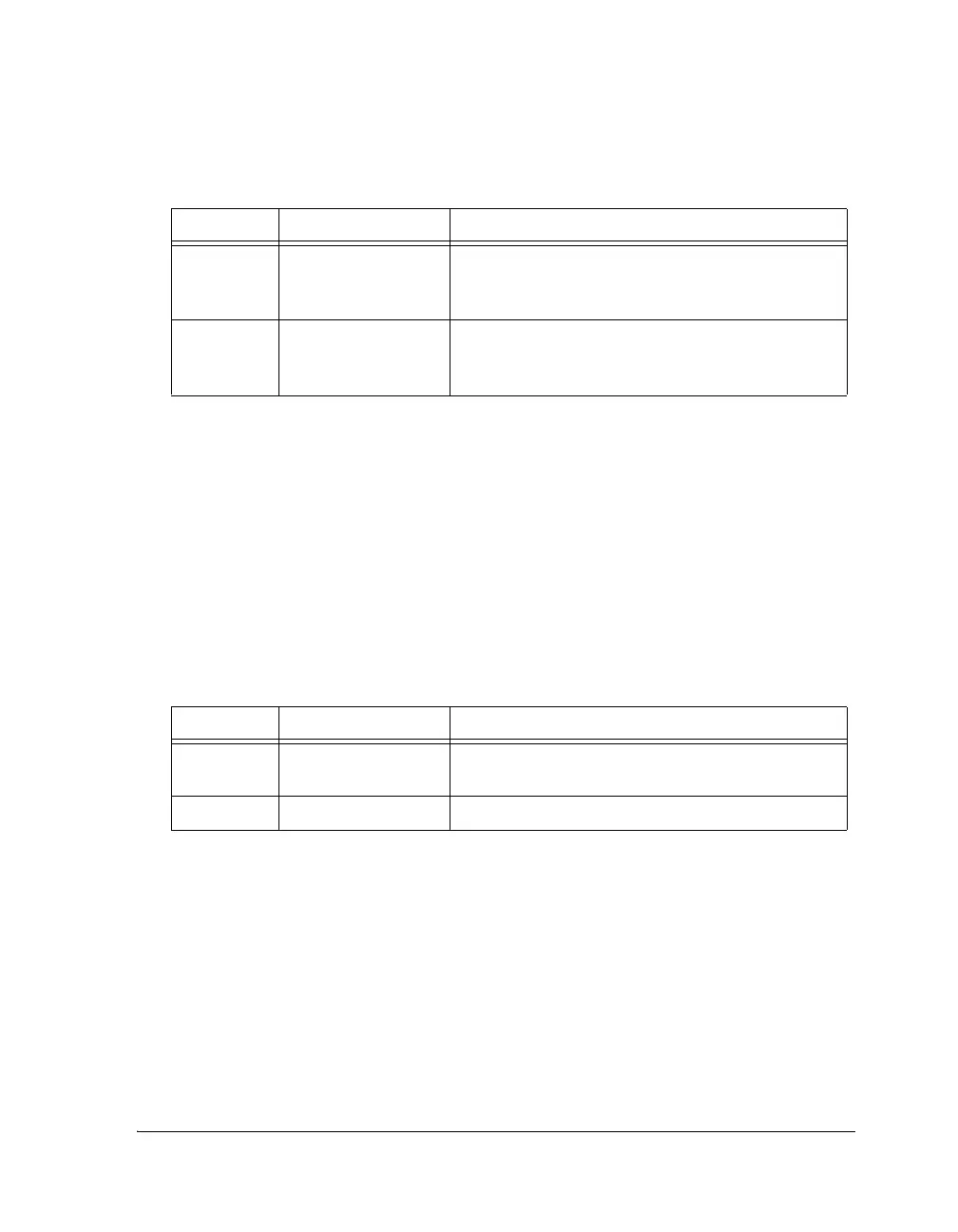

Table A-32. PWMDTx Register Bit Descriptions

Bit Name Description

9–0 PWMDT PWM Dead Time (unsigned). Program a time delay

setting of 0x0000 to 0x03FF. Default = 0

15–10 Reserved

Loading...

Loading...