ADSP-21368 SHARC Processor Hardware Reference 3-75

External Port

L

With external buffering enabled, each access takes one extra cycle.

SDRAM Read Optimization

To achieve better performance, read addresses can be provided in a predic-

tive manner to the SDRAM memory. This is done by setting (=1) the

SDROPT bit (bit 16) and correctly configuring the SDMODIFY bits (bits 20–

17) in the SDRRC register. The predictive address given to the memory

depends on the SDMODIFY bits values. If the SDMODIFY value is 2, then the

address + 2 is the predictive value provided to the SDRAM address pins.

Programs may choose to determine whether read optimization is used or

not. If read optimization is disabled, then each read takes 6 cycles for a

CAS latency of 2. With read optimization enabled, 32 sequential reads,

with offsets ranging from 0 to 15, take only 37 cycles. Read optimization

should not be enabled while reading at the external bank boundaries. For

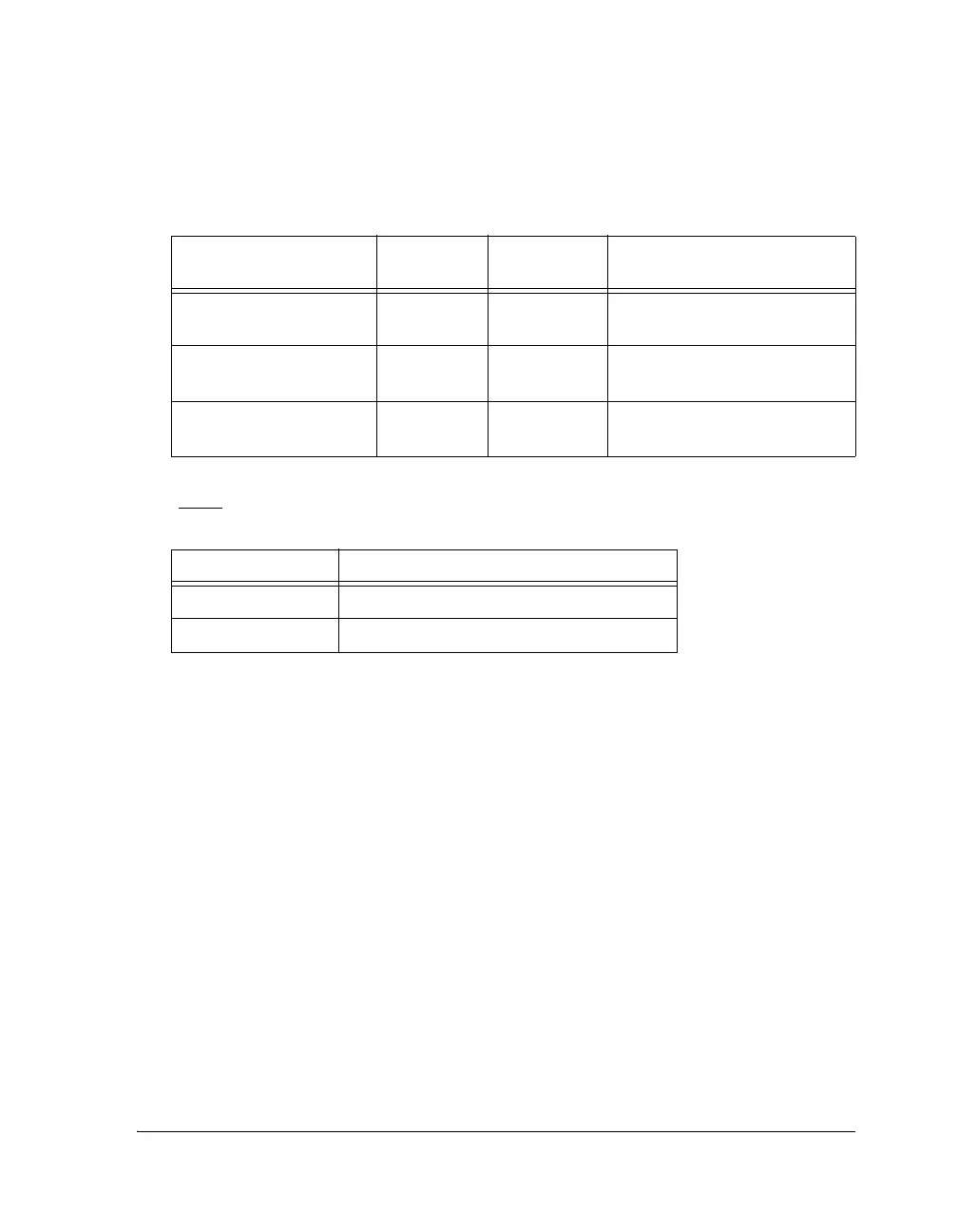

Table 3-28. Optimal Data Throughput for 16-Bit Data Accesses

(CAS Latency = 2)

Access Operation Page Throughput per SDCLK

(32-Bit Data)

Sequential and

uninterrupted

Read Same 32 words per 69 cycles

Sequential and uninter-

rupted

Write Same 2 cycles

Non Sequential and

uninterrupted

Read Same 7 cycles

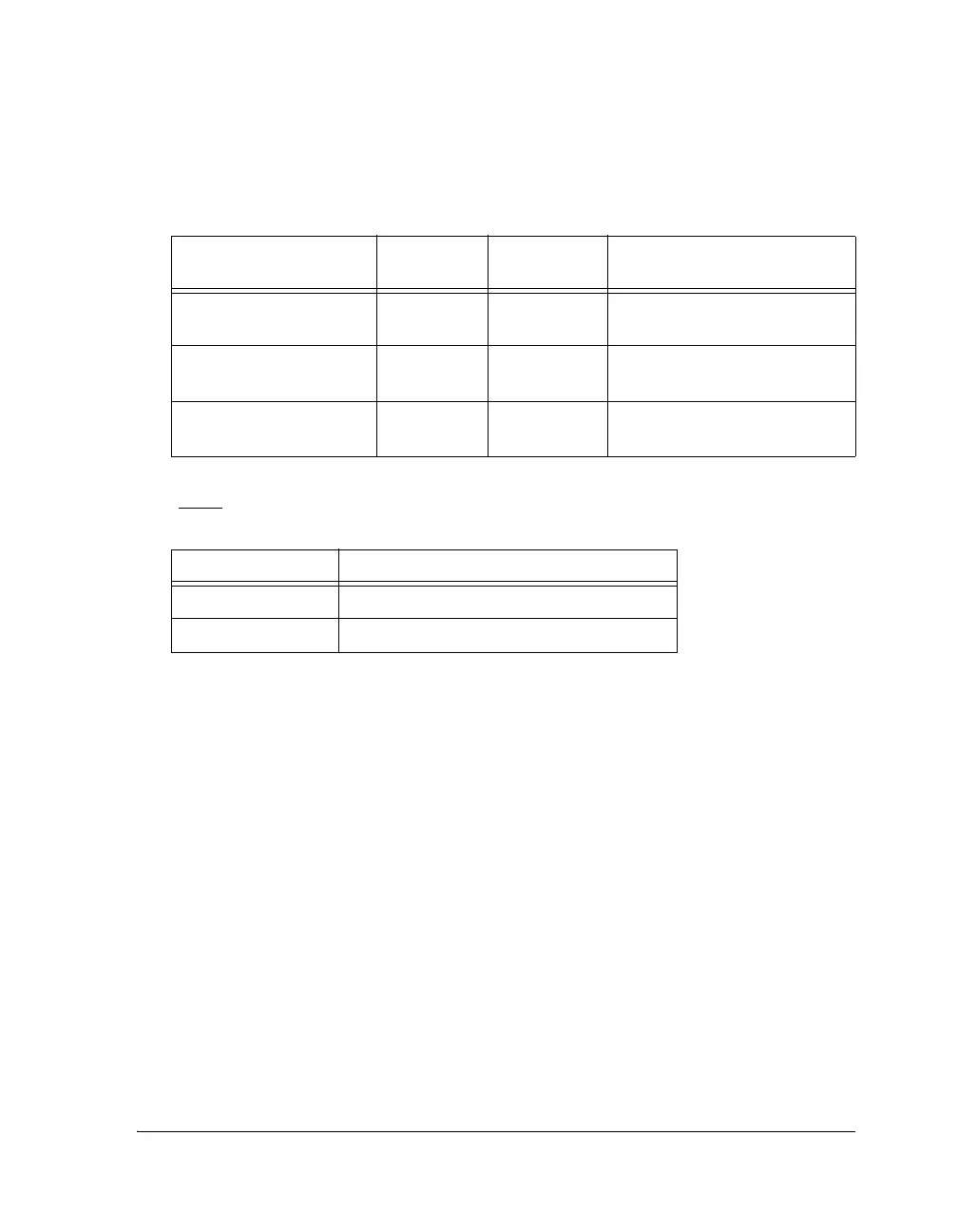

Table 3-29. Accesses Between External Memory Banks

(MSx, CAS Latency = 2)

Operation Idle Cycles per SDCLK (32-Bit Data)

Read 6 cycles

Write 1 cycle

Loading...

Loading...