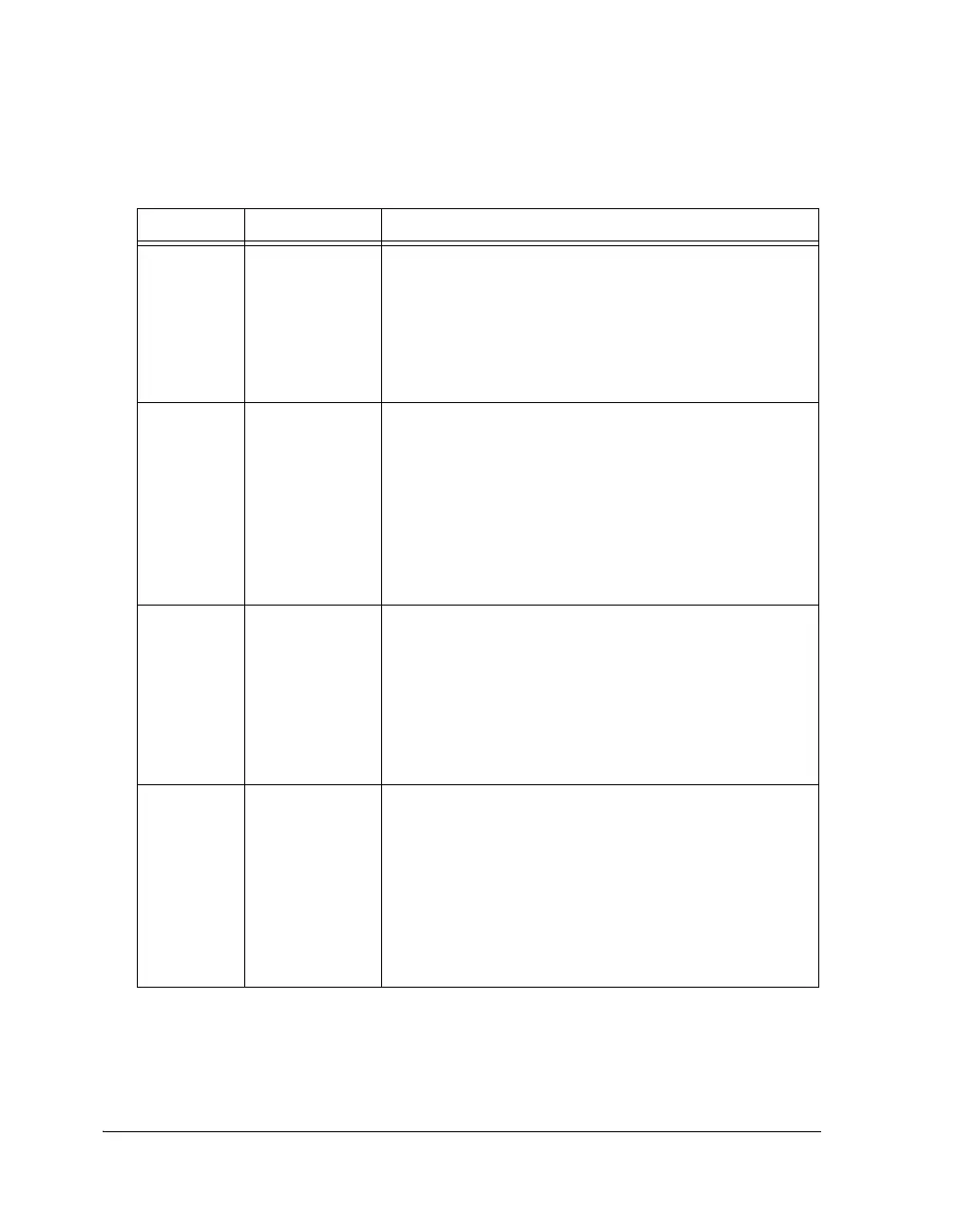

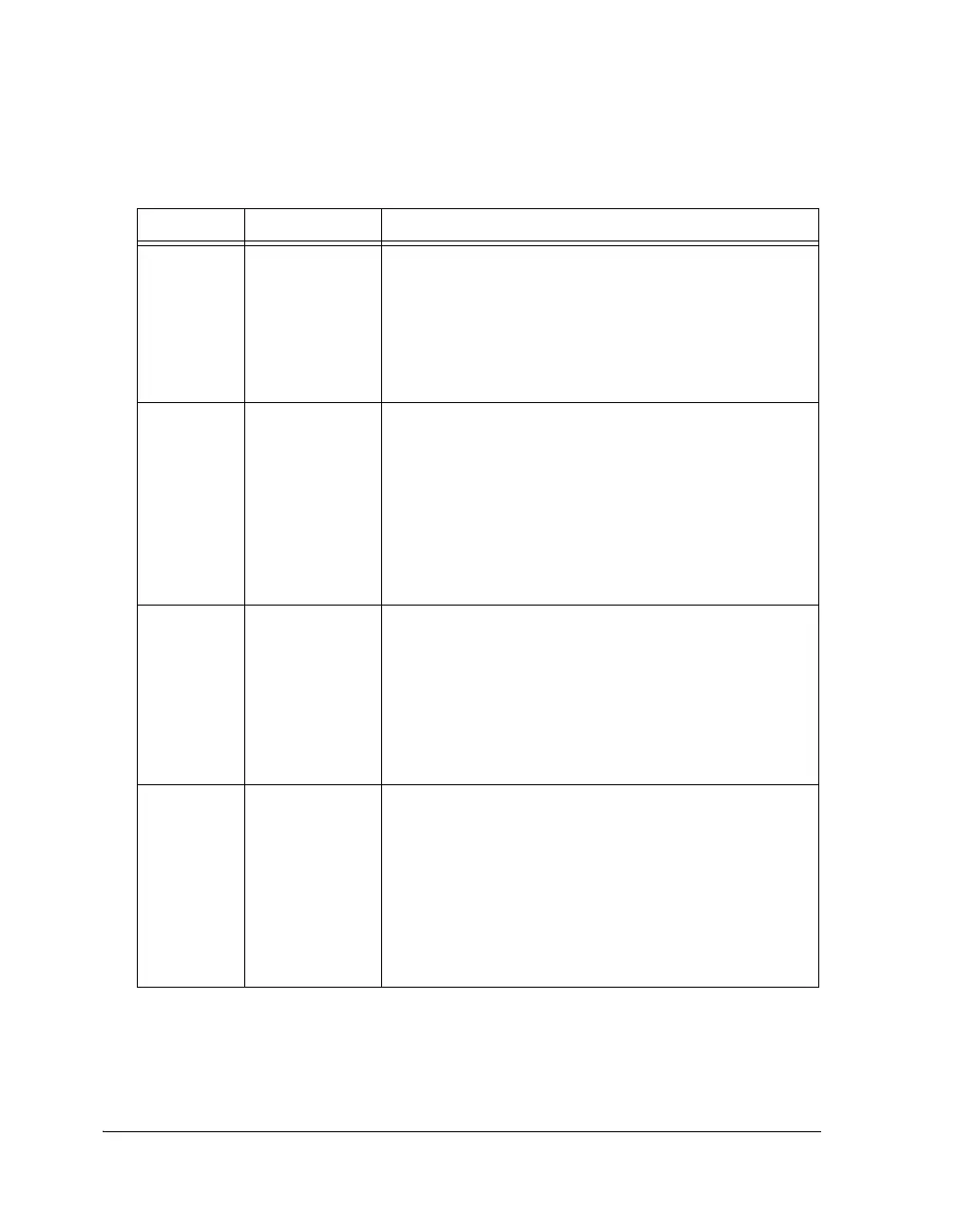

Two Wire Interface Registers

A-142 ADSP-21368 SHARC Processor Hardware Reference

5 TWIWERR Buffer Write Error.

0 = The current master receive has not detected a receive

buffer write error.

1 = The current master transfer was aborted due to a receive

buffer write error. The receive buffer and receive shift register

were both full at the same time. This bit is cleared by writing

a one to its bit location

6 TWISDASEN Serial Data Sense. For use when direct sensing of the serial

data line is required. The register value is delayed due to the

input filter (nominally 50 ns). Normal master and slave

mode operation should not require this feature.

0 = An inactive “one” is currently being sensed on serial data

line.

1 = An active “zero” is currently being sensed on serial data

line. The source of the active driver is not known and can be

internal or external.

7 TWISCLSEN Serial Clock Sense. For use when direct sensing of the serial

clock line is required. The register value is delayed due to the

input filter (nominally 50 ns). Normal master and slave

mode operation should not require this feature.

0 = An inactive “one” is currently being sensed on SCLK.

1 = An active “zero” is currently being sensed on SCLK. The

source of the active driver is not known and can be internal

or external.

8 TWIBUSY Bus Busy. Indicates whether the bus is currently busy or free.

This indication applies to all devices. Upon a START condi-

tion, setting the register value is delayed due to the input fil-

tering. Upon a STOP condition, clearing the register value

occurs after time t

BUF

.

0 = The bus is free. The clock and data bus signals have been

inactive for the appropriate bus free time.

1 = The bus is busy. Clock and/or data activity has been

detected.

Table A-58. Master Status Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...