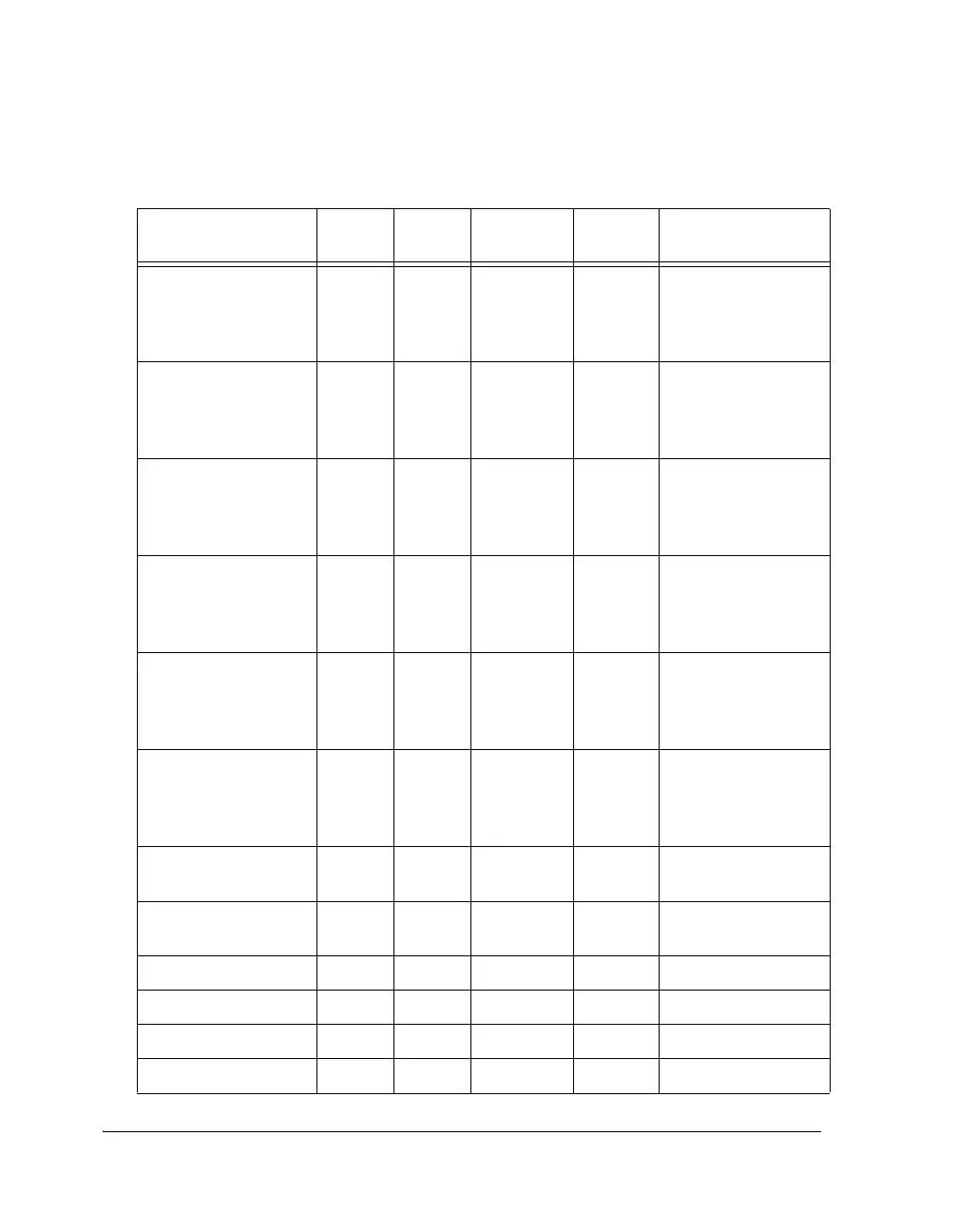

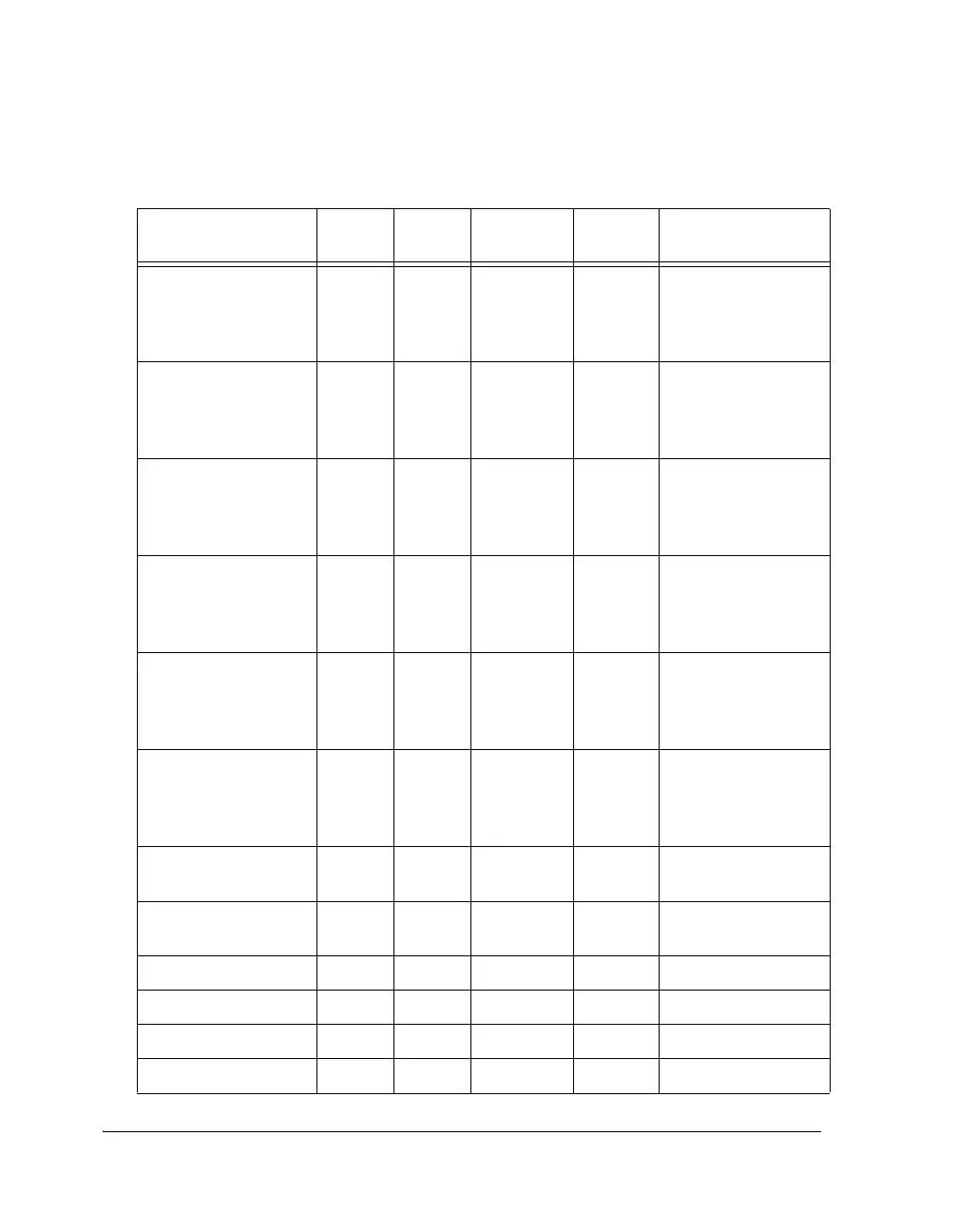

Configuring IOP/Core Interaction

2-10 ADSP-21368 SHARC Processor Hardware Reference

IRPTL/IMASK

(high priority option)

LIRPTL

(low priority option)

11

6

0x2C

0x5C

DAIHI

DAILI

18 IDP_FIF0

Channel 2

IRPTL/IMASK

(high priority option)

LIRPTL

(low priority option)

11

6

0x2C

0x5C

DAIHI

DAILI

19 IDP_FIF0

Channel 3

IRPTL/IMASK

(high priority option)

LIRPTL

(low priority option)

11

6

0x2C

0x5C

DAIHI

DAILI

20 IDP_FIF0

Channel 4

IRPTL/IMASK

(high priority option)

LIRPTL

(low priority option)

11

6

0x2C

0x5C

DAIHI

DAILI

21 IDP_FIF0

Channel 5

IRPTL/IMASK

(high priority option)

LIRPTL

(low priority option)

11

6

0x2C

0x5C

DAIHI

DAILI

22 IDP_FIF0

Channel 6

IRPTL/IMASK

(high priority option)

LIRPTL

(low priority option)

11

6

0x2C

0x5C

DAIHI

DAILI

23 IDP_FIF0

Channel 7

IRPTL/IMASK

(high priority option)

12 0x30 SPIHI 24 RXSPI, TXSPI

LIRPTL

(low priority option)

9 0x74 SPILI 25 RXSPIB, TXSPIB

IRPTL/IMASK 18 0x68 MTMI 26 MTM Read FIFO

IRPTL/IMASK UART0RXI 27 RBR0

IRPTL/IMASK UART1RXI 28 RBR1

IRPTL/IMASK UART0TXI 29 THR0

Table 2-3. Default DMA Interrupt Vector Locations (Cont’d)

Associated Register(s) Bits Vector

Address

Interrupt

Name

DMA

Channel

Data Buffer

Loading...

Loading...