ADSP-21368 SHARC Processor Hardware Reference 2-9

I/O Processor

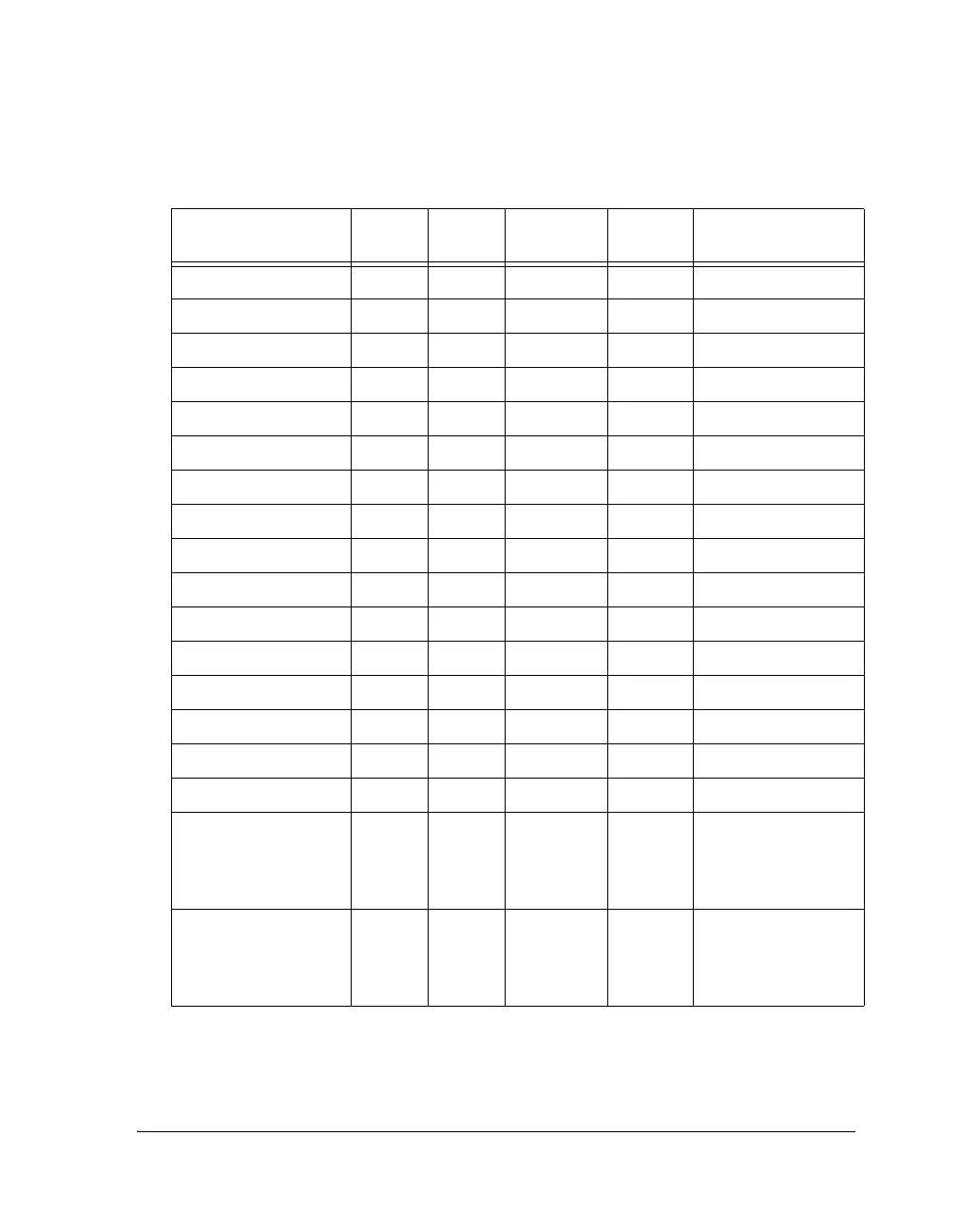

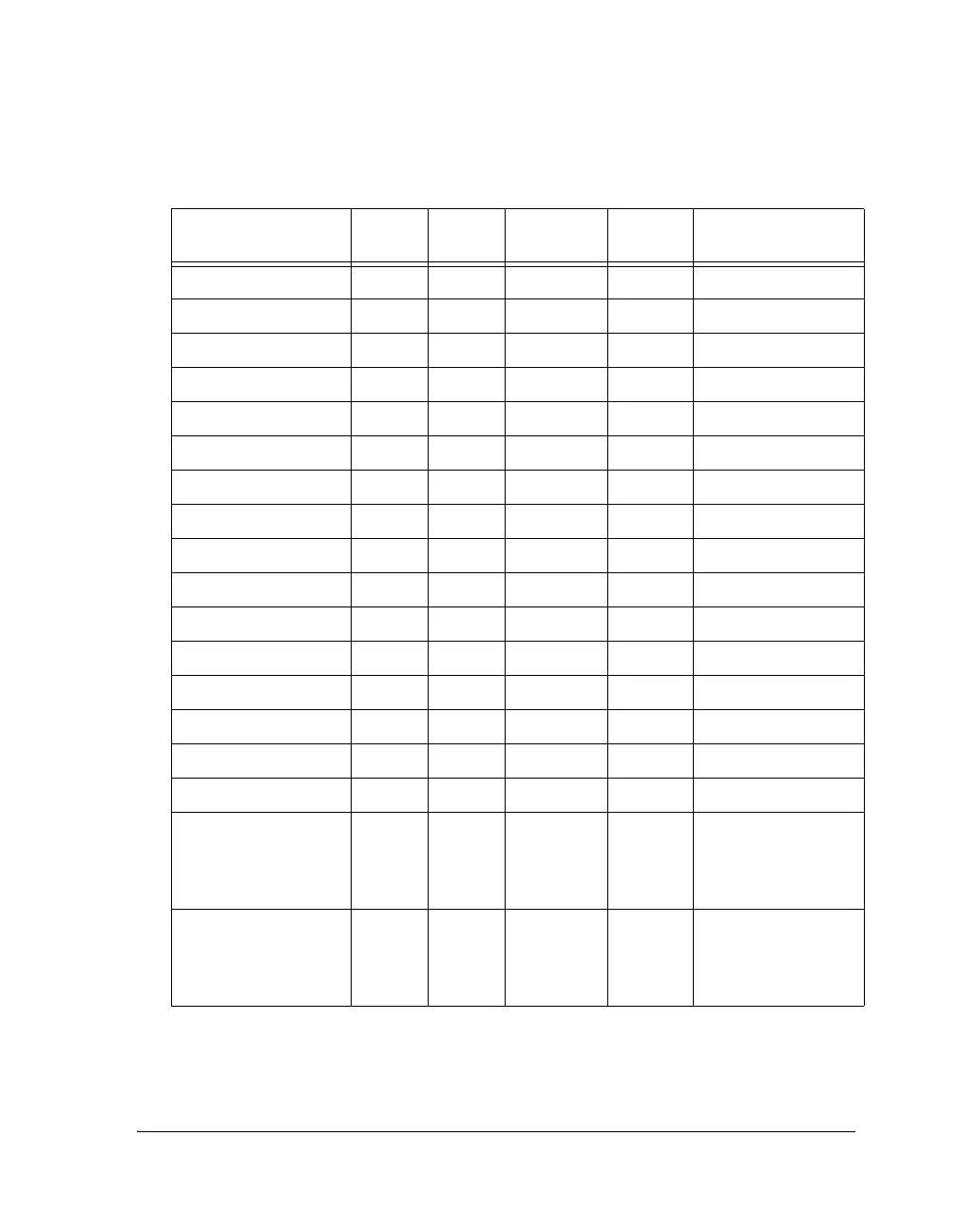

Table 2-3. Default DMA Interrupt Vector Locations

Associated Register(s) Bits Vector

Address

Interrupt

Name

DMA

Channel

Data Buffer

IRPTL/IMASK 14 0x38 SP1I 0 RXSP1A, TXSP1A

LIRPTL 0 0x44 SP0I 2 RXSP0A, TXSP0A

IRPTL/IMASK 15 0x3C SP3I 4 RXSP3A, TXSP3A

LIRPTL 1 0x48 SP2I 6 RXSP2A, TXSP2A

IRPTL/IMASK 16 0x40 SP5I 8 RXSP5A, TXSP5A

LIRPTL 2 0x4C SP4I 10 RXSP4A, TXSP4A

IRPTL/IMASK 5 0x58 SP7I 12 RXSP7A, TXSP7A

LIRPTL 19 0x6C SP6I 14 RXSP6A, TXSP6A

IRPTL/IMASK 14 0x38 SP1I 1 RXSP1B, TXSP1B

LIRPTL 0 0x44 SP0I 3 RXSP0B, TXSP0B

IRPTL/IMASK 15 0x3C SP3I 5 RXSP3B, TXSP3B

LIRPTL 1 0x48 SP2I 7 RXSP2B, TXSP2B

IRPTL/IMASK 16 0x40 SP5I 9 RXSP5B, TXSP5B

LIRPTL 2 0x4C SP4I 11 RXSP4B, TXSP4B

IRPTL/IMASK 5 0x58 SP7I 13 RXSP7B, TXSP7B

LIRPTL 19 0x6C SP6I 15 RXSP6B, TXSP6B

IRPTL/IMASK

(high priority option)

LIRPTL

(low priority option)

11

6

0x2C

0x5C

DAIHI

DAILI

16 IDP_FIF0

Channel 0

IRPTL/IMASK

(high priority option)

LIRPTL

(low priority option)

11

6

0x2C

0x5C

DAIHI

DAILI

17 IDP_FIF0

Channel 1

Loading...

Loading...