ADSP-21368 SHARC Processor Hardware Reference B-19

Interrupts

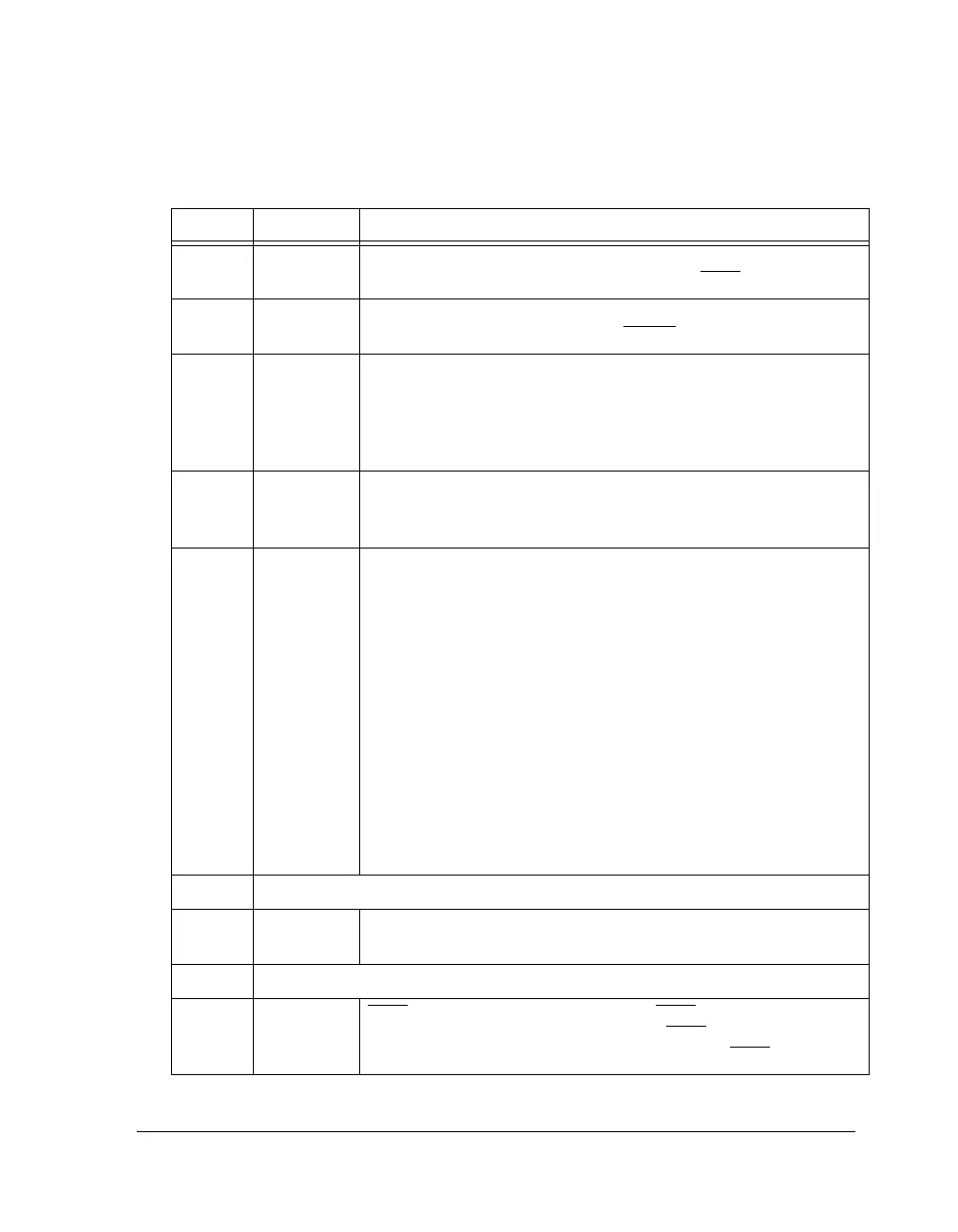

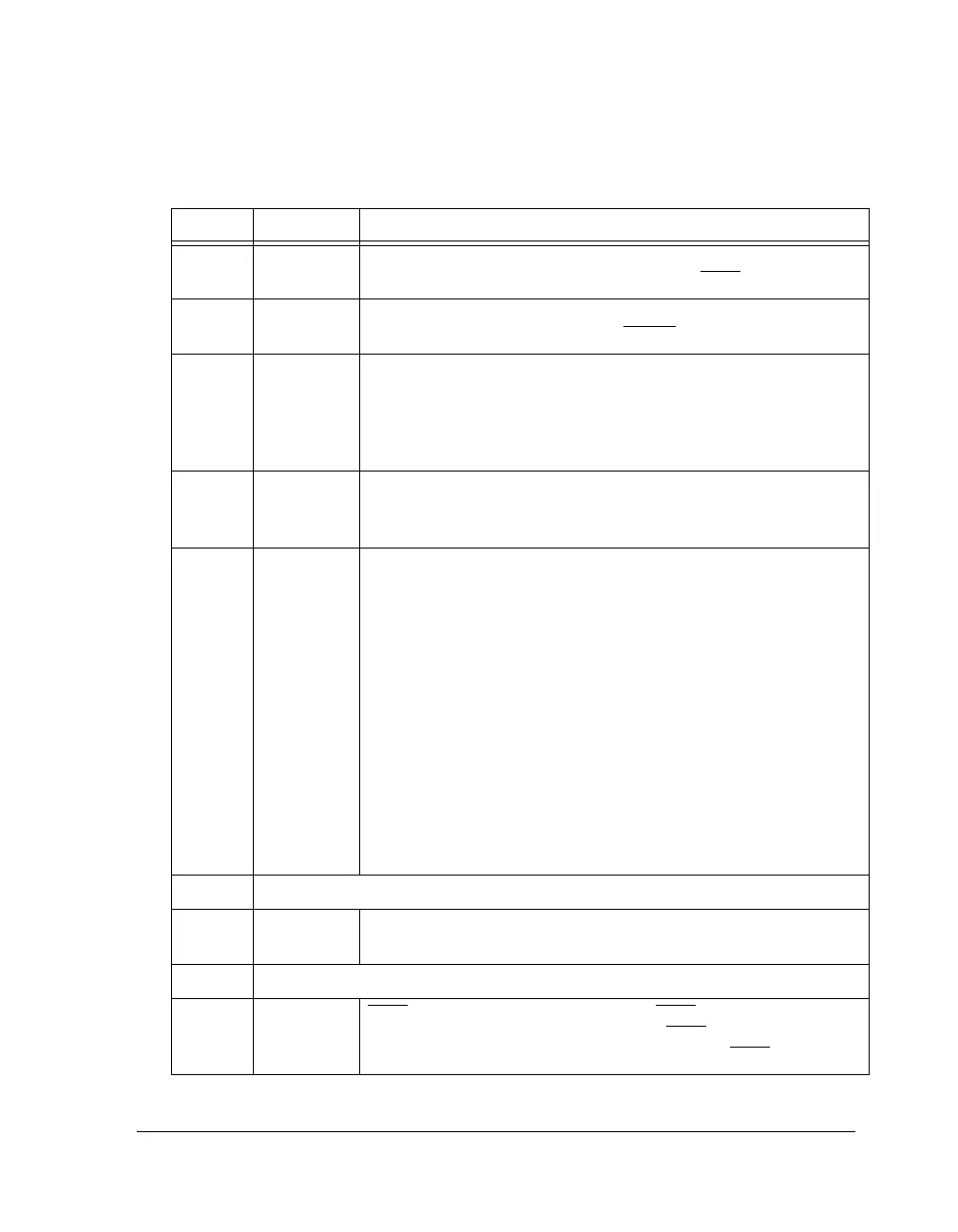

Table B-6. IMASK Register Bit Descriptions

Bit Name Description

0EMUIEmulator Interrupt. This bit is set to 1 (unmasked). An EMUI occurs

on reset and when an external device asserts the EMU pin.

1RSTIReset Interrupt. This bit is set to 1 (unmasked). An RSTI occurs on

reset as an external device asserts the RESET pin.

2 IICDI Illegal Input Condition Detected Interrupt. Unmasks the IICDI inter-

rupt (if set, = 1), or masks (if cleared, = 0). An IICDI occurs when a

true results from the logical ORing of the illegal I/O processor register

access (IIRA) and unaligned 64-bit memory access bits in the STKYx

registers.

3SOVFIStack Overflow/Full Interrupt. Unmasks the SOVFI interrupt

(if set, = 1), or masks the SOVFI interrupt (if cleared, = 0). An SOVFI

occurs when a stack in the program sequencer overflows or is full.

4TMZHITimer Expired High Priority. Unmasks the TMZHI interrupt

(if set, = 1), or masks the TMZHI interrupt (if cleared, = 0). A TMZHI

occurs when the timer decrements to zero. Note that this event also

triggers a TMZLI. The timer operations are controlled as follows:

• The TCOUNT register contains the timer counter. The timer

decrements the TCOUNT register each clock cycle.

• The TPERIOD value specifies the frequency of timer inter-

rupts. The number of cycles between interrupts is

TPERIOD + 1. The maximum value of TPERIOD is 2

32

– 1.

• The TIMEN bit in the MODE2 register starts and stops the

timer.

Since the timer expired event (TCOUNT decrements to zero) generates

two interrupts, TMZHI and TMZLI, programs should unmask the

timer interrupt with the desired priority and leave the other one

masked.

5Reserved

6BKPIHardware Breakpoint Interrupt. Unmasks the BKPI interrupt

(if set, = 1), or masks the BKPI interrupt (if cleared, = 0).

7Reserved

8IRQ2IIRQ2

Hardware Interrupt. Unmasks the IRQ2I interrupt (if set, = 1),

or masks the interrupt (if cleared, = 0). An IRQ2

I occurs when an

external device asserts the FLAG2 pin configured as IRQ2

.

Loading...

Loading...