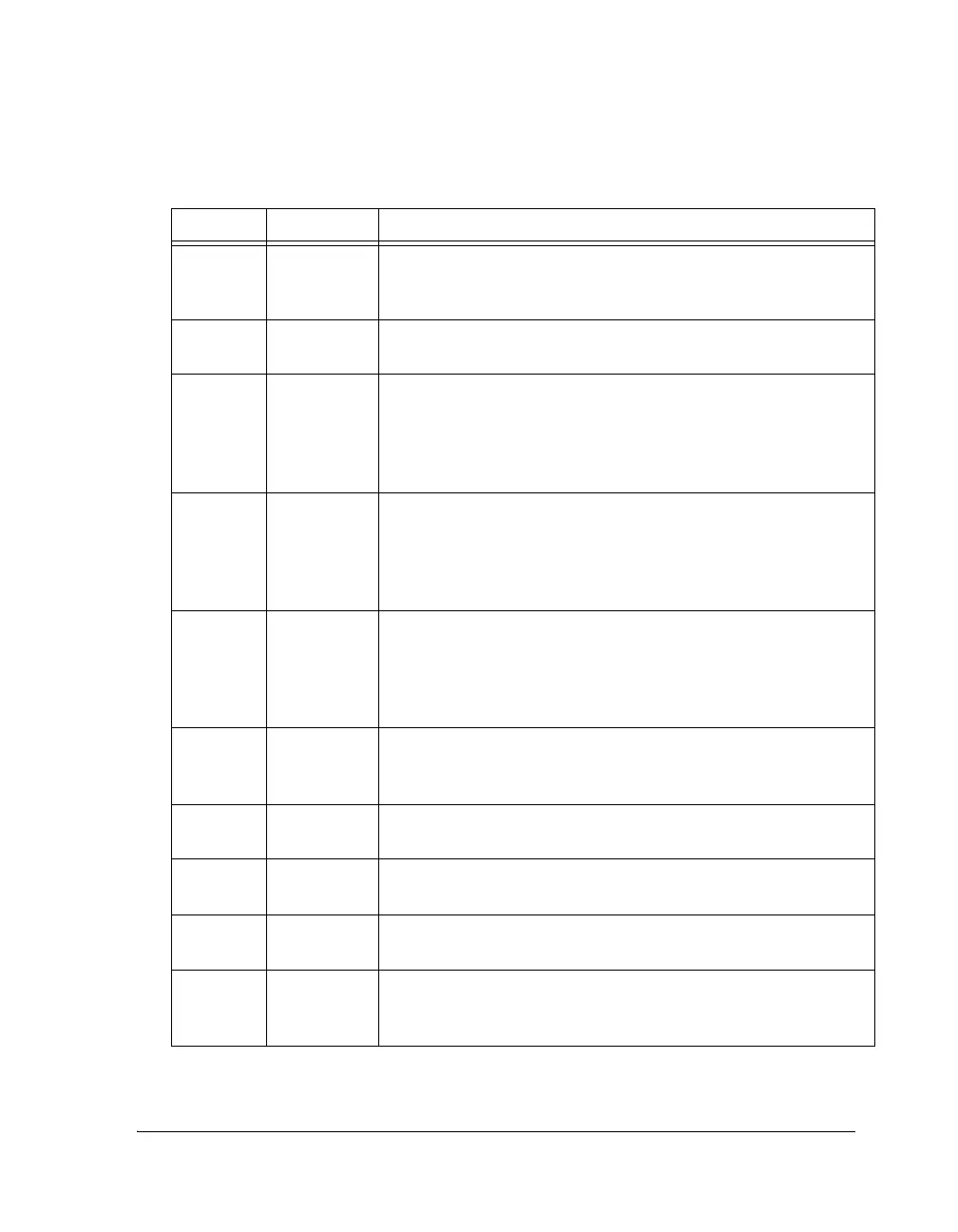

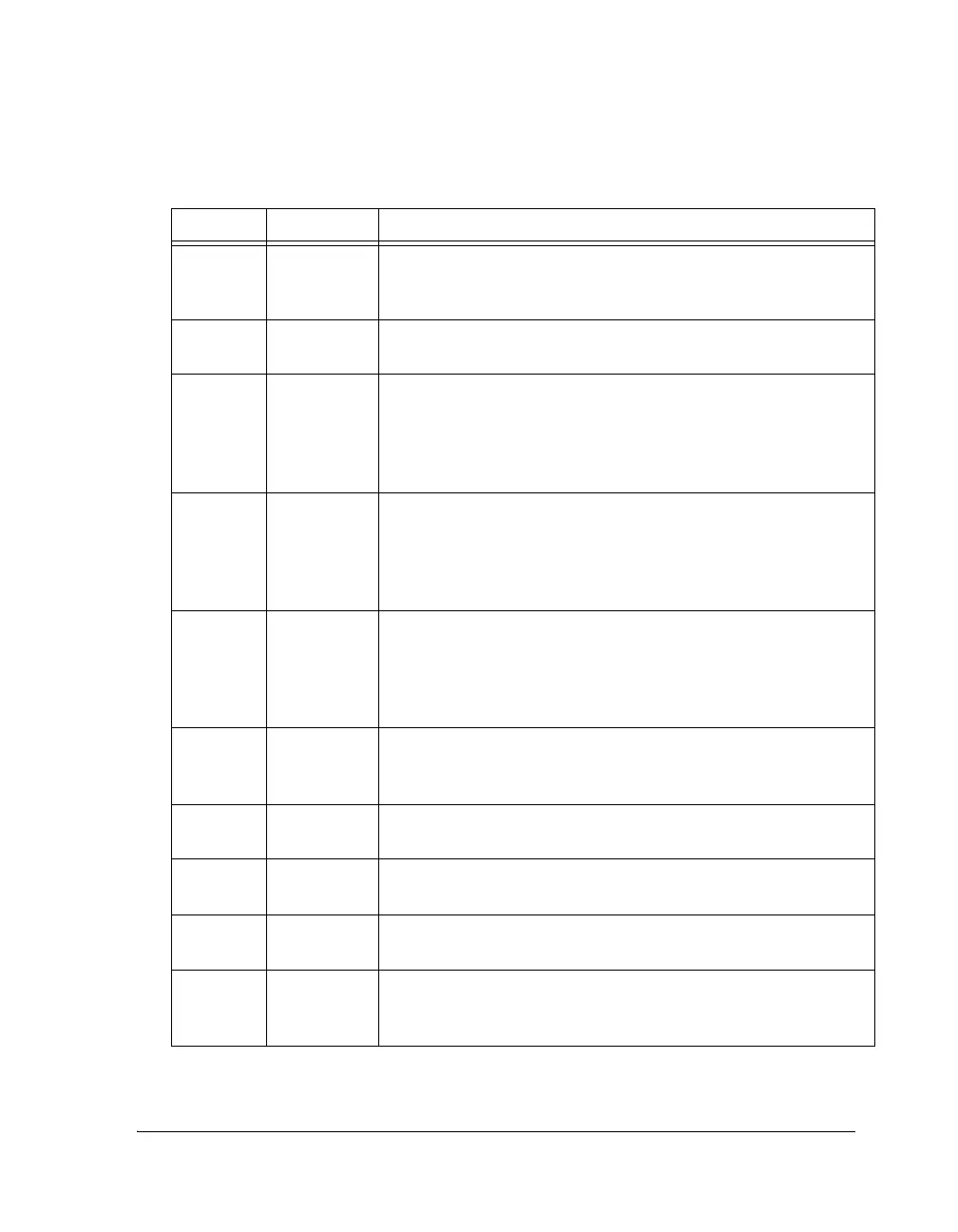

ADSP-21368 SHARC Processor Hardware Reference B-17

Interrupts

17 P14I (DPI) Programmable Interrupt 14. Indicates if a DPI interrupt is latched

and is pending (if set, = 1), or no DPI interrupt is pending (if cleared,

= 0).

18 P15I

(MTMDMA)

Programmable Interrupt 15 (MTMDMA Interrupt).

19 P16I (SP6I) Programmable Interrupt 16. Indicates if an SP6I interrupt is latched

and is pending (if set, = 1), or no SP6I is pending (if cleared, = 0). An

SP6I interrupt occurs two cycles after the last bit of an input/output

serial word is latched into/from RXSP6A/TXSP6A,

RXSP6B/TXSP6B.

20 CB7I DAG1 Circular Buffer 7 Overflow Interrupt. Indicates if a CB7I is

latched and is pending (if set, = 1), or no CB7I interrupt is pending

(if cleared, = 0). A circular buffer overflow occurs when the DAG cir-

cular buffering operation increments the I register past the end of the

buffer.

21 CB15I DAG2 Circular Buffer 15 Overflow Interrupt. Indicates if a CB15I

is latched and is pending (if set, = 1), or no CB15I is pending (if

cleared, = 0). A circular buffer overflow occurs when the DAG circu-

lar buffering operation increments the I register past the end of the

buffer.

22 TMZLI Timer Expired (Low Priority) Interrupt. Indicates if a TMZLI is

latched and is pending (if set, = 1), or no TMZLI is pending (if

cleared, = 0). For more information, see “TMZHI” on page B-15.

23 FIXI Fixed-Point Overflow Interrupt. Indicates if a FIXI is latched and is

pending (if set, = 1), or no FIXI is pending (if cleared, = 0).

24 FLTOI Floating-Point Overflow Interrupt. Indicates if a FLTOI is latched

and is pending (if set, = 1), or no FLTOI is pending (if cleared, = 0).

25 FLTUI Floating-Point Underflow Interrupt. Indicates if a FLTUI is latched

and is pending (if set, = 1), or no FLTUI is pending (if cleared, = 0).

26 FLTII Floating-Point Invalid Operation Interrupt. This bit

indicates if a FLTII is latched and is pending (if set, = 1), or no FLTII

is pending (if cleared, = 0).

Table B-5. Interrupt Latch (IRPTL) Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...