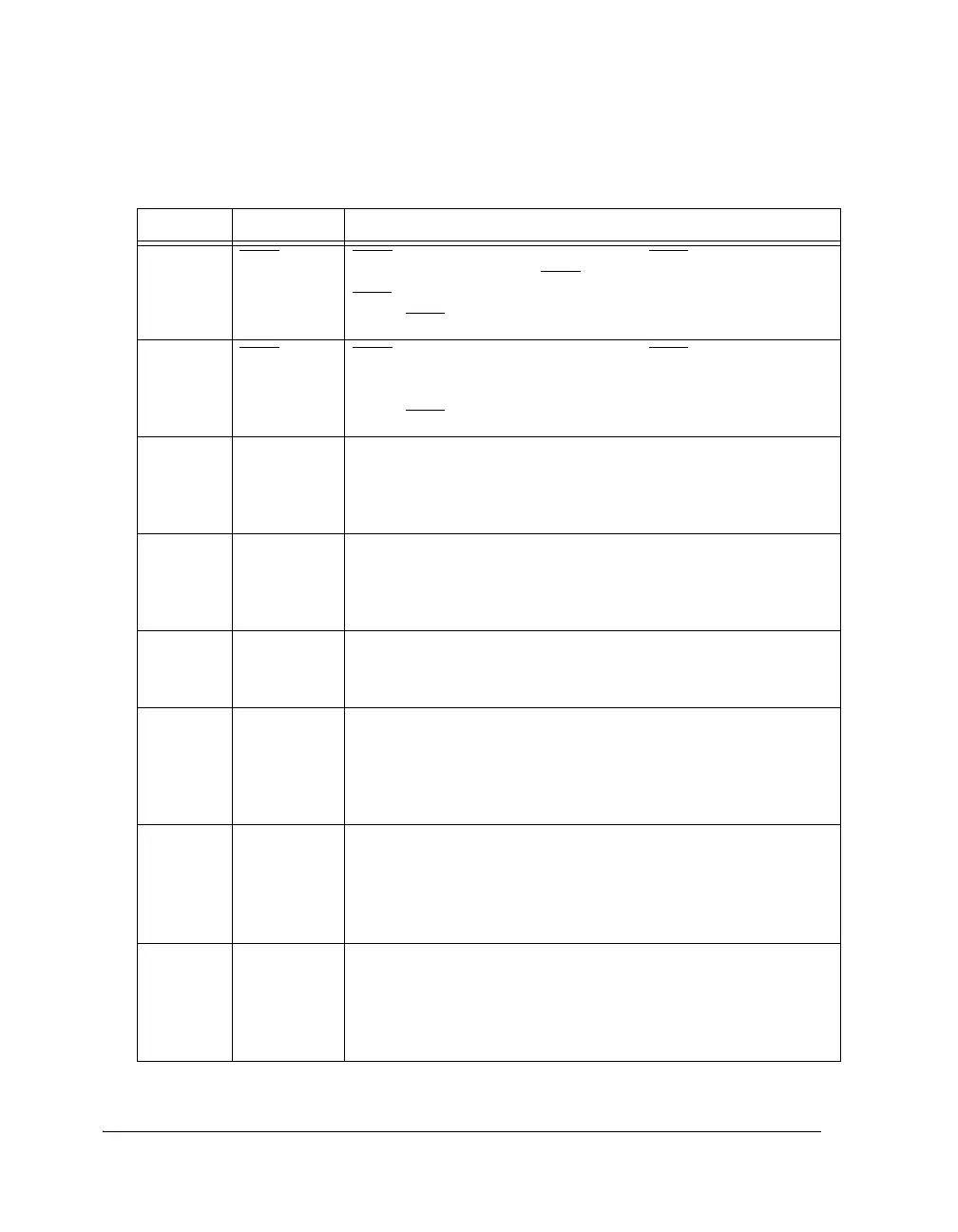

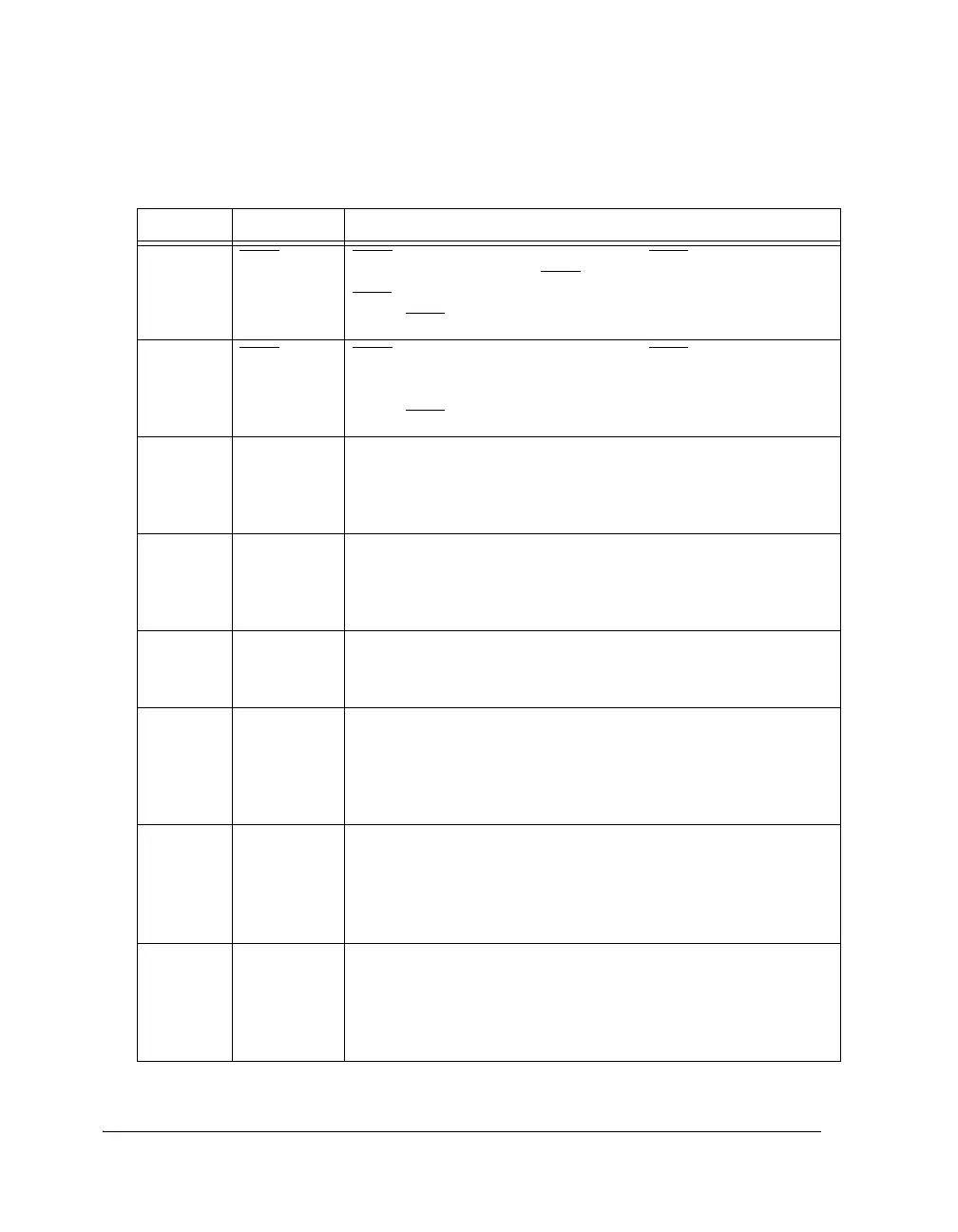

Interrupt Registers

B-16 ADSP-21368 SHARC Processor Hardware Reference

9IRQ1I IRQ1 Hardware Interrupt. Indicates if an IRQ1I is latched and is

pending (if set, = 1), or no IRQ1I is pending (if cleared, = 0). An

IRQ1I occurs when an external device asserts the FLAG1 pin config-

ured as IRQ1

.

10 IRQ0I IRQ0 Hardware Interrupt. Indicates if an IRQ0I is latched and is

pending (if set, = 1), or no IRQ0I is pending (if cleared, = 0). An

IRQ0I occurs when an external device asserts the FLAG0 pin config-

ured as IRQ0

.

11 P0I

(DAI1I)

Programmable Interrupt 0 (DAI High Priority Interrupt). Indicates

if a DAI1I interrupt is latched and is pending (if set, = 1), or no

DAI1I interrupt is pending (if cleared, = 0). This is the higher prior-

ity option.

12 P1I

(SPIAI)

Programmable Interrupt 1 (SPI Transmit or Receive High Priority

Interrupt). Indicates if an interrupt in the primary SPIAI is latched

and is pending (if set, = 1), or no interrupt is pending (if cleared, =

0). This is the higher priority option.

13 P2I

(GPTMR0I)

Programmable Interrupt 2 (General-Purpose IOP Timer 0 Inter-

rupt). Indicates if a GPTMR0I is latched and is pending (if set, = 1),

or no GPTMR0I is pending (if cleared, = 0).

14 P3I (SP1I) Programmable Interrupt 3 (SPORT 1 Interrupt). Indicates if an

SP1I interrupt is latched and is pending (if set, = 1), or no SP1I is

pending (if cleared, = 0). An SP1I interrupt occurs two cycles after

the last bit of an input/output serial word is latched into/from

RXSP1A/TXSP1A, RXSP1B/TXSP1B.

15 P4I (SP3I) Programmable Interrupt 4 (SPORT 3 Interrupt). Indicates if an

SP3I interrupt is latched and is pending (if set, = 1), or no SP3I is

pending (if cleared, = 0). An SP3I interrupt occurs two cycles after

the last bit of an input/output serial word is latched into/from

RXSP3A/TXSP3A, RXSP3B/TXSP3B.

16 P5I (SP5I) Programmable Interrupt 5 (SPORT 5 Interrupt). Indicates if an

SP5I interrupt is latched and is pending (if set, = 1), or no SP5I is

pending (if cleared, = 0). An SP5I interrupt occurs two cycles after

the last bit of an input/output serial word is latched into/from

RXSP5A/TXSP5A, RXSP5B/TXSP5B.

Table B-5. Interrupt Latch (IRPTL) Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...