Two Wire Interface Registers

A-146 ADSP-21368 SHARC Processor Hardware Reference

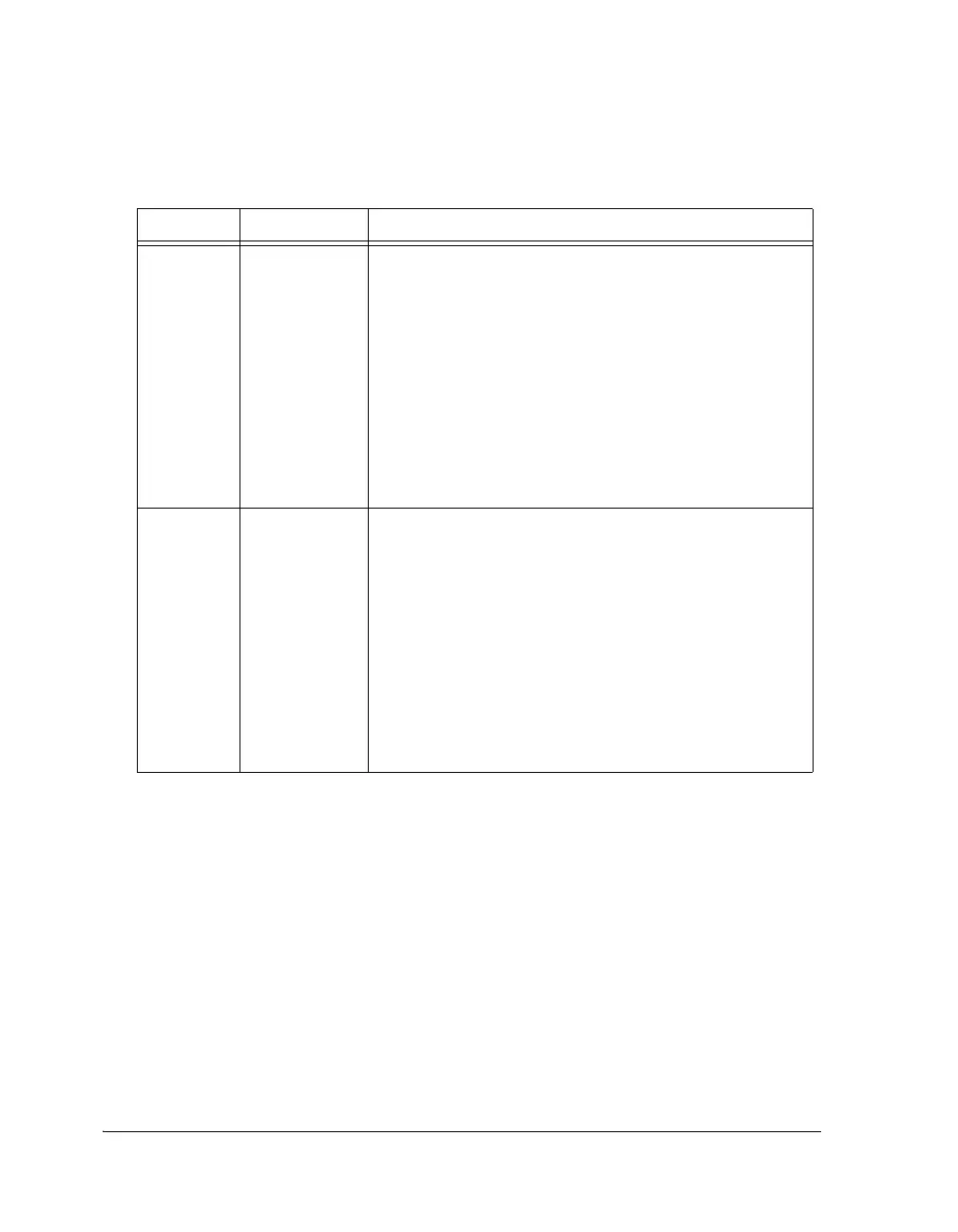

Table A-60. FIFO Status Register Bit Descriptions

Bit Name Description

1–0 TWITXS Transfer FIFO Status. These read-only bits indicate the num-

ber of valid data bytes in the FIFO buffer. The status is

updated with each FIFO buffer write using the peripheral data

bus or read access by the transmit shift register. Simultaneous

accesses are allowed.

00 = FIFO is empty. Either a single- or double-byte peripheral

write of the FIFO goes through immediately.

01 = FIFO contains one byte of data. A single byte peripheral

write of the FIFO goes through immediately. A double-byte

peripheral write waits until the FIFO is empty

11 = FIFO is full and contains two bytes of data.

10 = Illegal

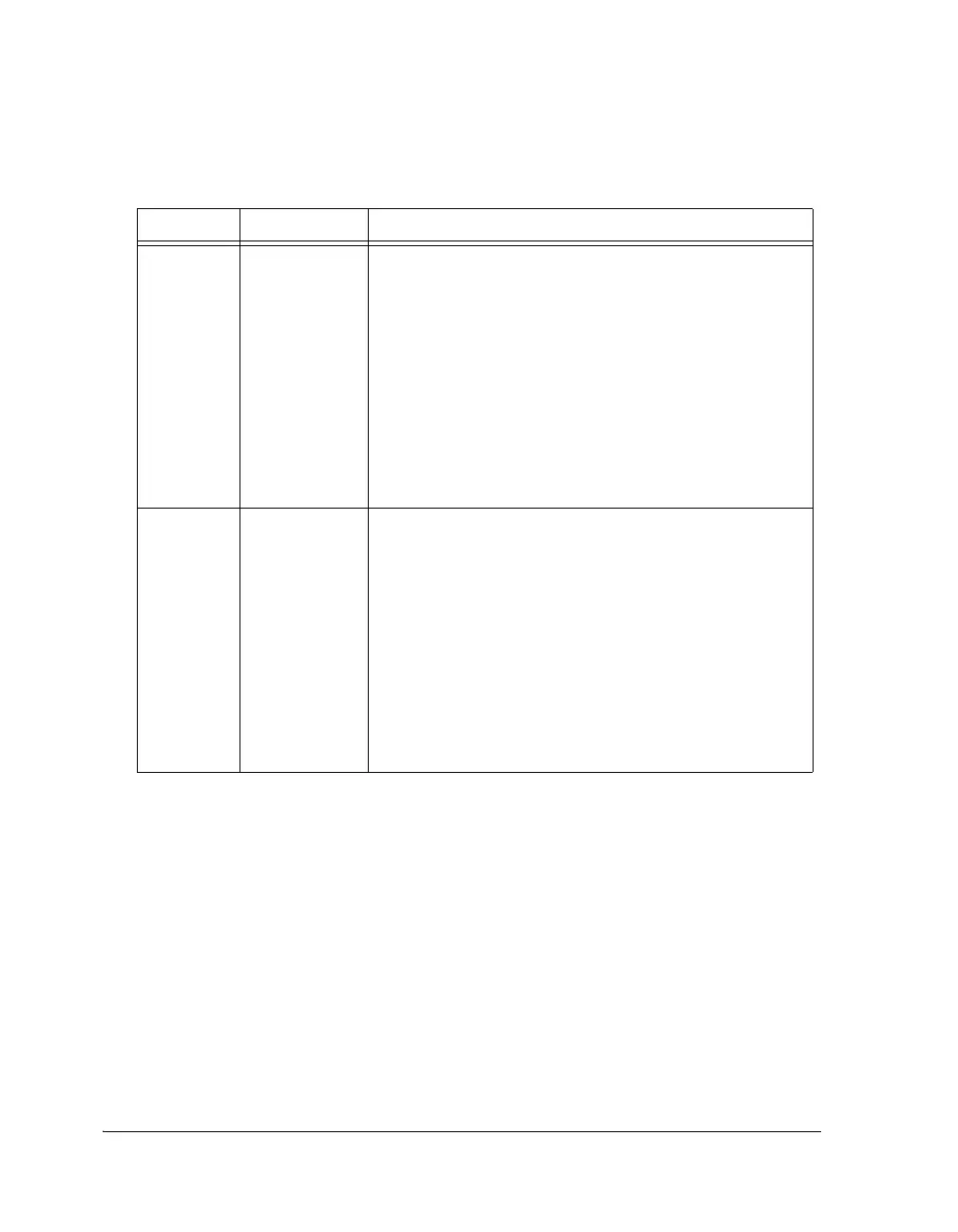

3–2 TWIRXS Receive FIFO Status. These read-only bits indicate the num-

ber of valid data bytes in the receive FIFO buffer. The status is

updated with each FIFO buffer read using the peripheral data

bus or write access by the receive shift register. Simultaneous

accesses are allowed.

00 = FIFO is empty

01 = FIFO contains one byte of data. A single-byte peripheral

read of the FIFO goes through immediately. A double-byte

peripheral read waits until the FIFO is full.

11 = FIFO is full and contains two bytes of data. Either a sin-

gle- or double-byte peripheral read of the FIFO is allowed.

10 = Illegal

Loading...

Loading...