Programming Examples

12-20 ADSP-21368 SHARC Processor Hardware Reference

The tasks performed at each interrupt are:

•

TWITXINT interrupt

This interrupt is generated every time the transmit FIFO has one

or two byte locations available to be written. To service this inter-

rupt, write a byte or word into the transmit FIFO registers (TXTWI8

or TXTWI16). During one of these interrupts (preferably the first

time), do the following:

•Set the RSTART bit (or earlier when TWIMCTL register is pro-

grammed first).

•Set the TWIMDIR bit to indicate the next transfer direction is

receive. This should be done before the addressing phase of

the next transfer begins.

•

TWIMCOMP interrupt

This interrupt is generated because all data has been transferred

(DCNT = 0). If no errors were generated, a start condition is initi-

ated. At this time, program the following bits of TWI_MASTER_CTRL

register:

•Clear RSTART (if this is the last transfer).

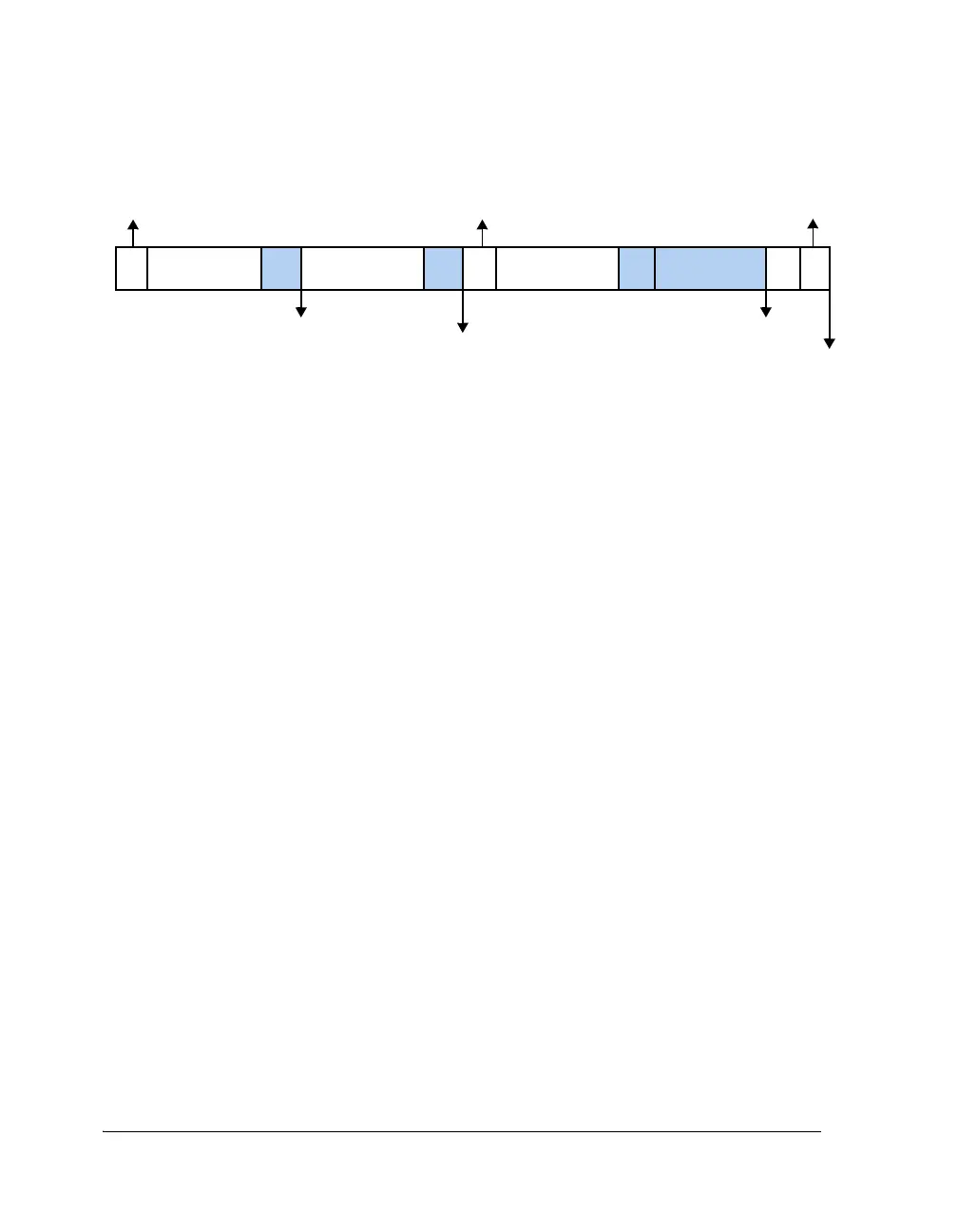

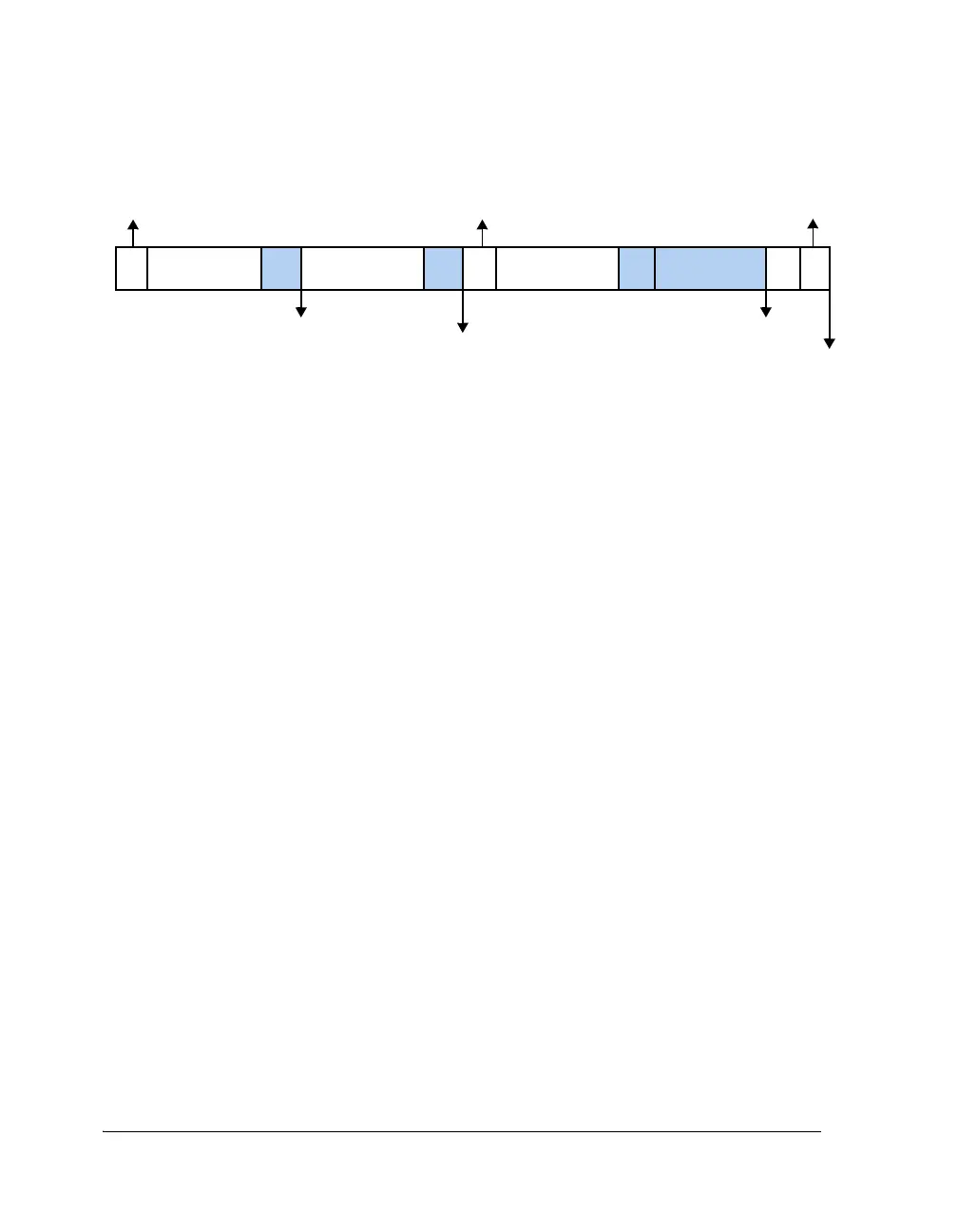

Figure 12-8. Transmit/Receive Data Repeated Start

7-BIT ADDRESS 7-BIT ADDRESSS ACK 8-BIT DATA 8-BIT DATAACK ACKSPACK

TWITXINT INTERRUPT

START

TWIMCOM INTERRUPT

TWIMCOM INTERRUPT

TWIRXINT INTERRUPT

REPEATED

START

STOP

Shaded region indicates slave to master transmission.

Loading...

Loading...