ADSP-21368 SHARC Processor Hardware Reference A-119

Register Reference

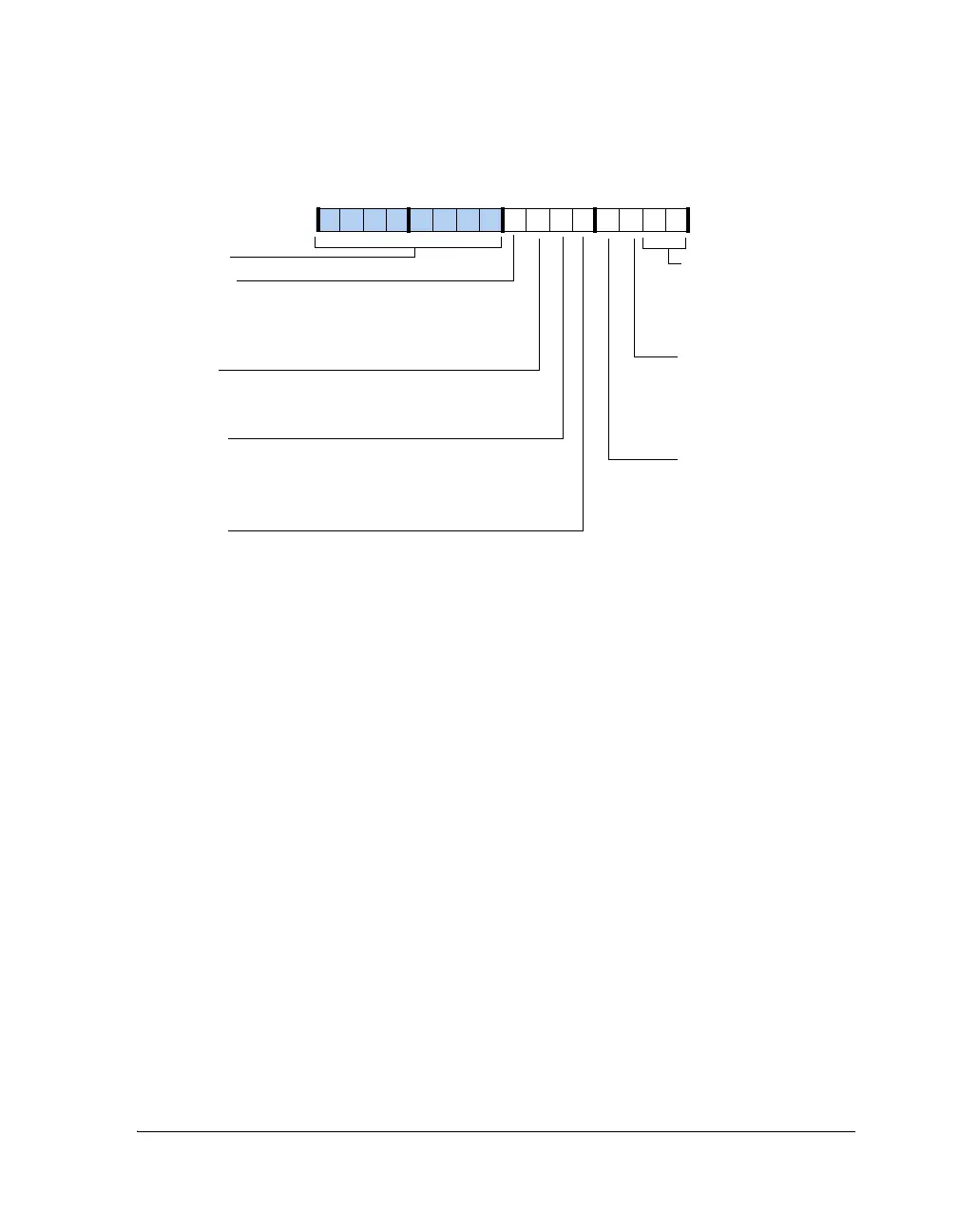

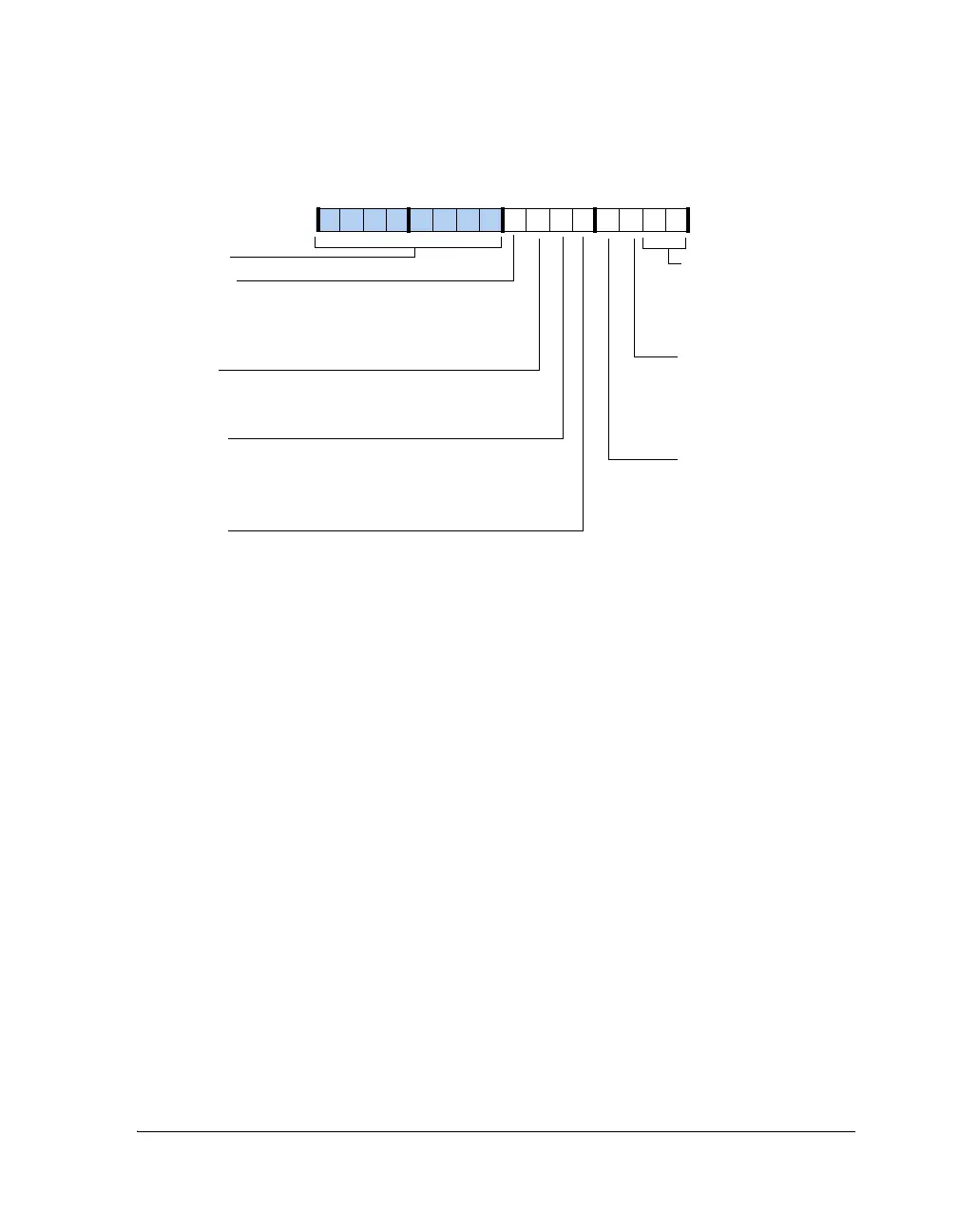

Figure A-48. UART Line Control Registers

15 14 13 12 11 10 8 7 6 5 4 3 2 1 0

0000000000000000

Reserved

UARTWLS

Word Length Select

00=5-bit word(UARTWLS5)

01=6-bit word(UARTWLS6)

10=7-bit word(UARTWLS7)

11=8-bit word(UARTWLS8)

UARTSTB

Stop Bits

1=2 stop bits for non-5-bit

word length or 1 1/2 stop bits

for 5-bit word length

0=1 stop bit

UARTSB

Stick Parity

Forces parity to defined value if set and PEN = 1

1=Parity transmitted and checked as 0

0=Parity transmitted and checked as 1

UARTSTP

UARTPEN

Parity Enable

1=Transmit and check parity

0=Parity not transmitted or

checked

UARTEPS

Set Break

1=Force Tx pin to 0

0=No force

9

UARTDLAB

Divisor Latch Access

1=Enable access to UARTxDLL and UARTxDLH

0=Enable access to UARTxTHR, UARTxRBR, and

UART_IER

Even Parity Select

1=Even parity

0=Odd parity when PEN = 1 and STP = 0

UART0LCR (0x3C03)

UART1LCR (0x4003)

Loading...

Loading...