ADSP-21368 SHARC Processor Hardware Reference 14-49

System Design

Master boot mode is used when the processor is booting from an

SPI-compatible serial PROM, serial FLASH, or slave host processor. The

specifics of booting from these devices are discussed individually. On

reset, the interface starts up in master mode performing a 384 32-bit word

DMA transfer.

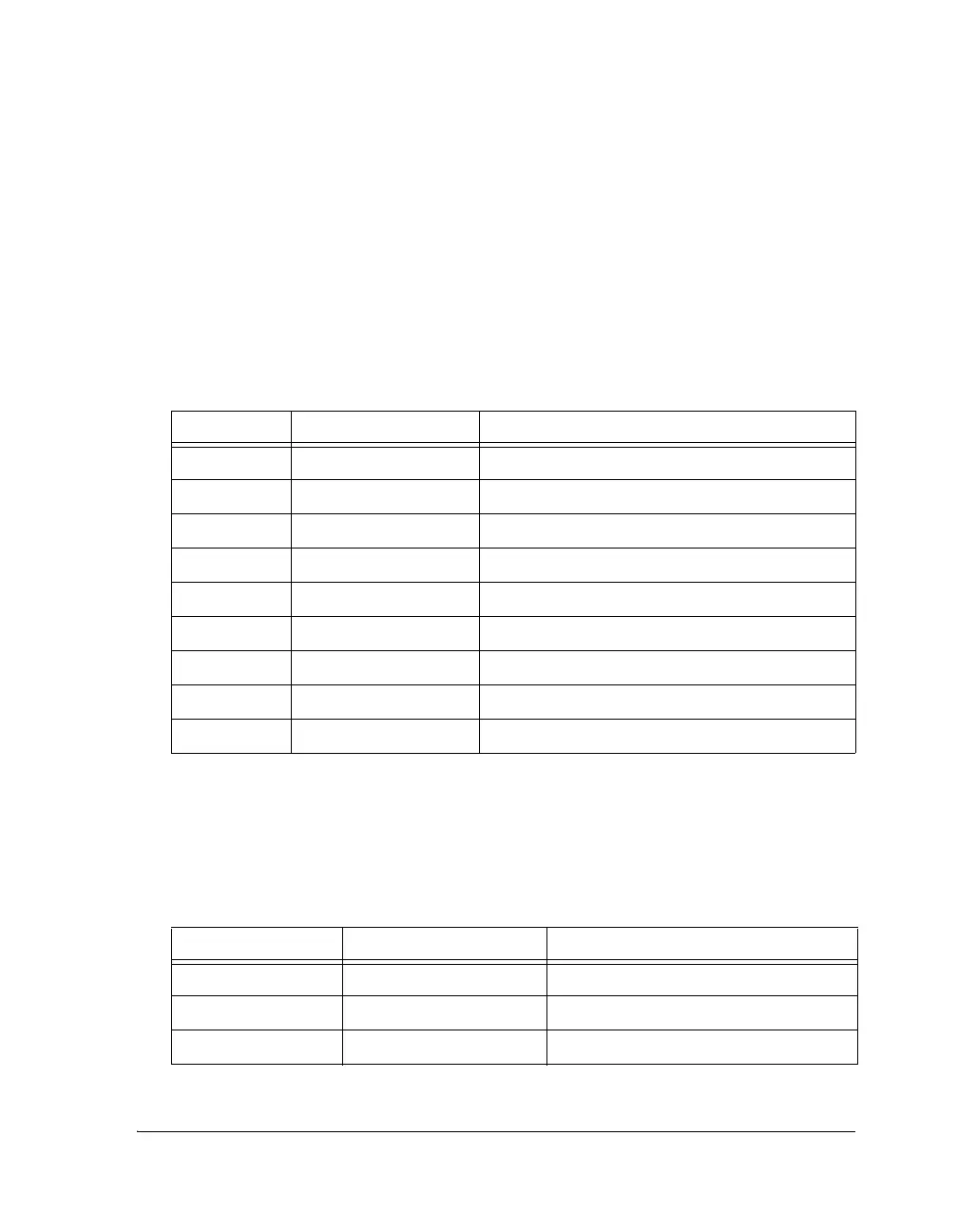

SPI master booting uses the default bit settings shown in Table 14-13.

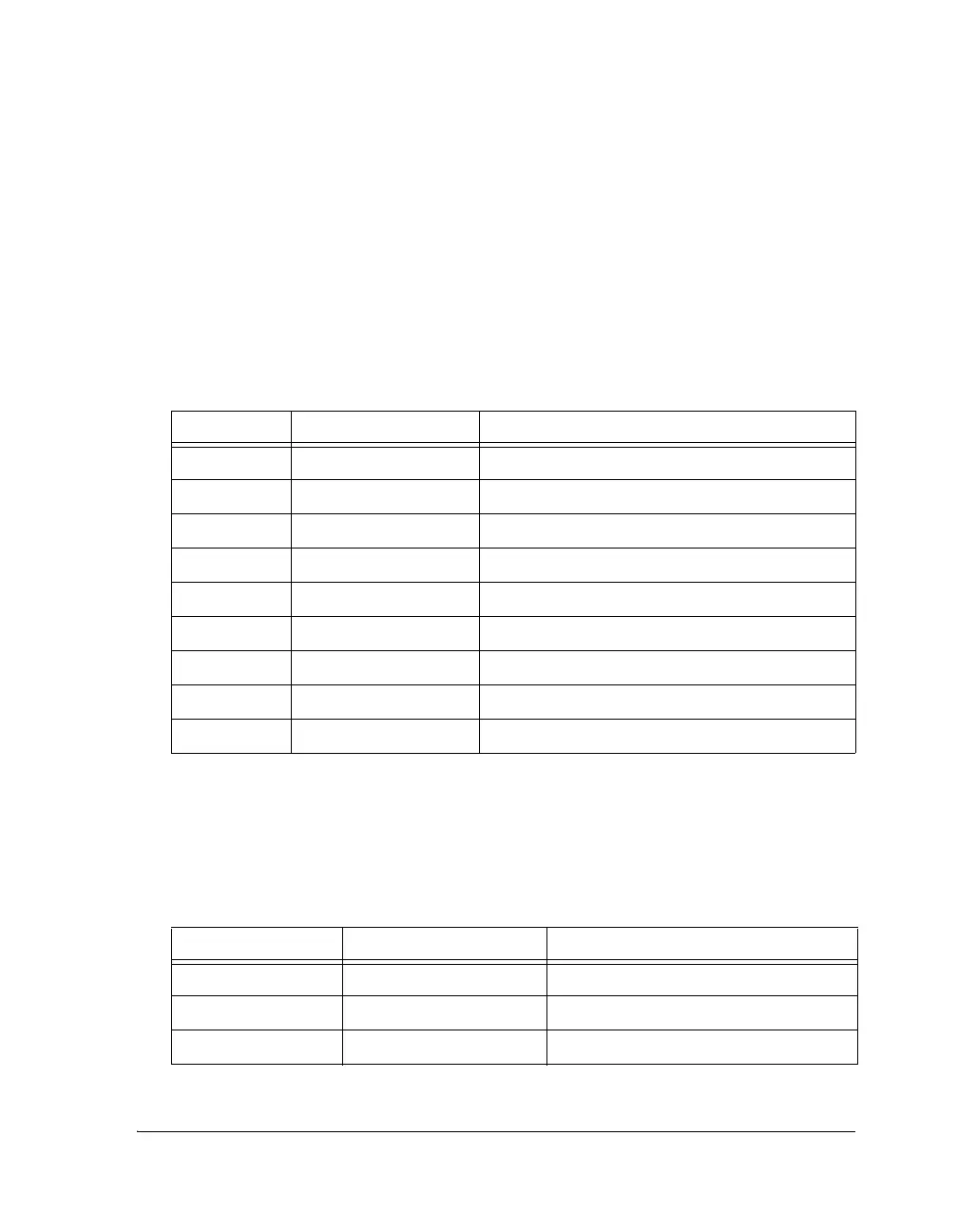

The SPI DMA channel is used when downloading the boot kernel infor-

mation to the processor. At reset, the DMA parameter registers are

initialized to the values listed in Table 14-14.

Table 14-13. SPI Master Boot Mode Bit Settings

Bit Setting Comment

SPIEN Set (= 1) SPI Enabled

SPIMS Set (= 1) Master device

MSBF Cleared (= 0) LSB first

WL 10 32-bit SPI receive shift register word length

DMISO Cleared (= 0) MISO enabled

SENDZ Set (= 1) Send zeros

SPIRCV Set (= 1) Receive DMA enabled

CLKPL Set (= 1) Active low SPI clock

CPHASE Set (= 1) Toggle SPICLK at the beginning of the first bit

Table 14-14. Parameter Initialization Value for Master Boot

Parameter Register Initialization Value Comment

SPICTL 0x0000 5D06

SPIBAUD 0x0064 CCLK/400 =500 KHz@ 200 MHz

SPIFLG 0xfe01 FLAG0 used as slave-select

Loading...

Loading...