Power Management Control Register (PMCTL)

A-174 ADSP-21368 SHARC Processor Hardware Reference

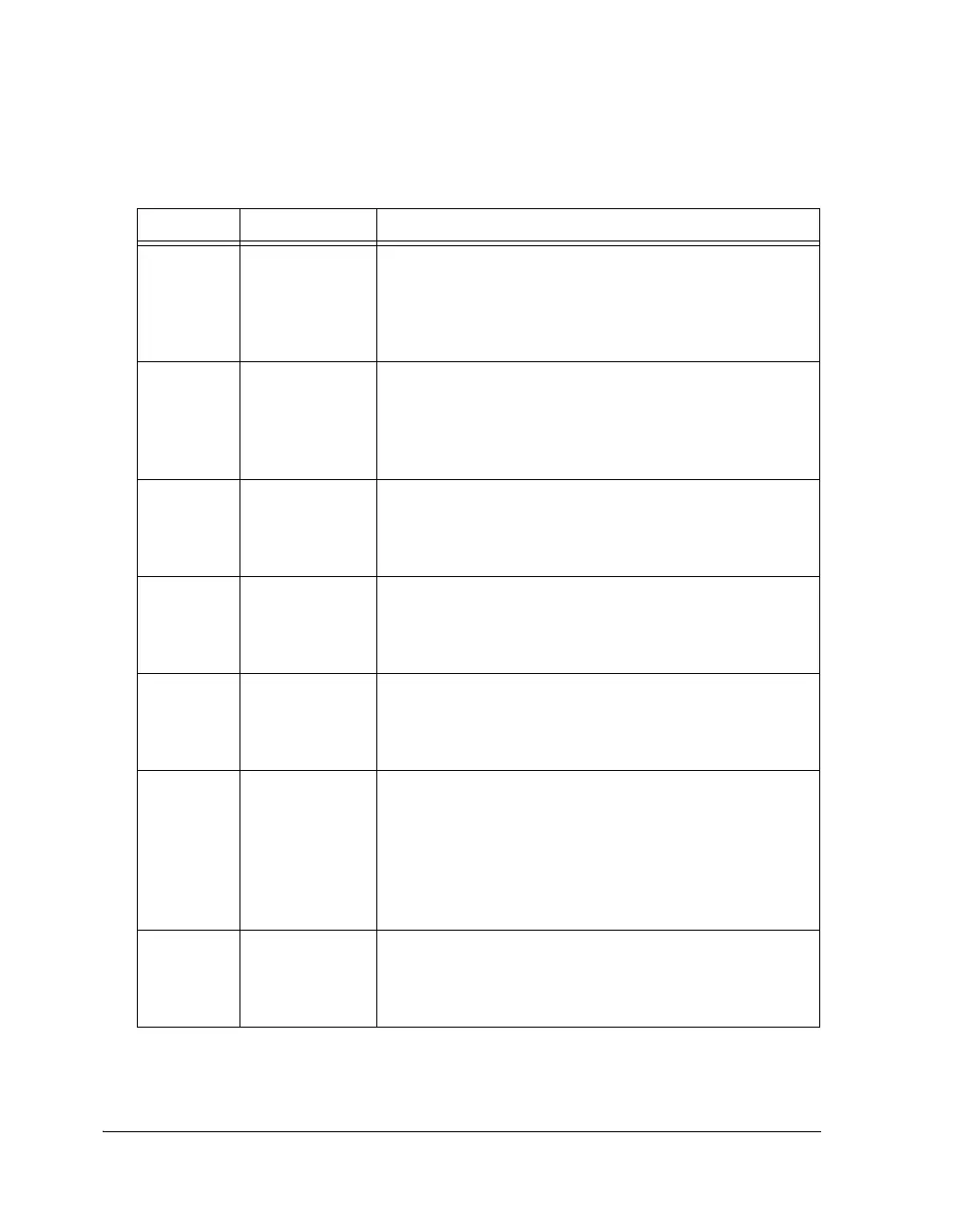

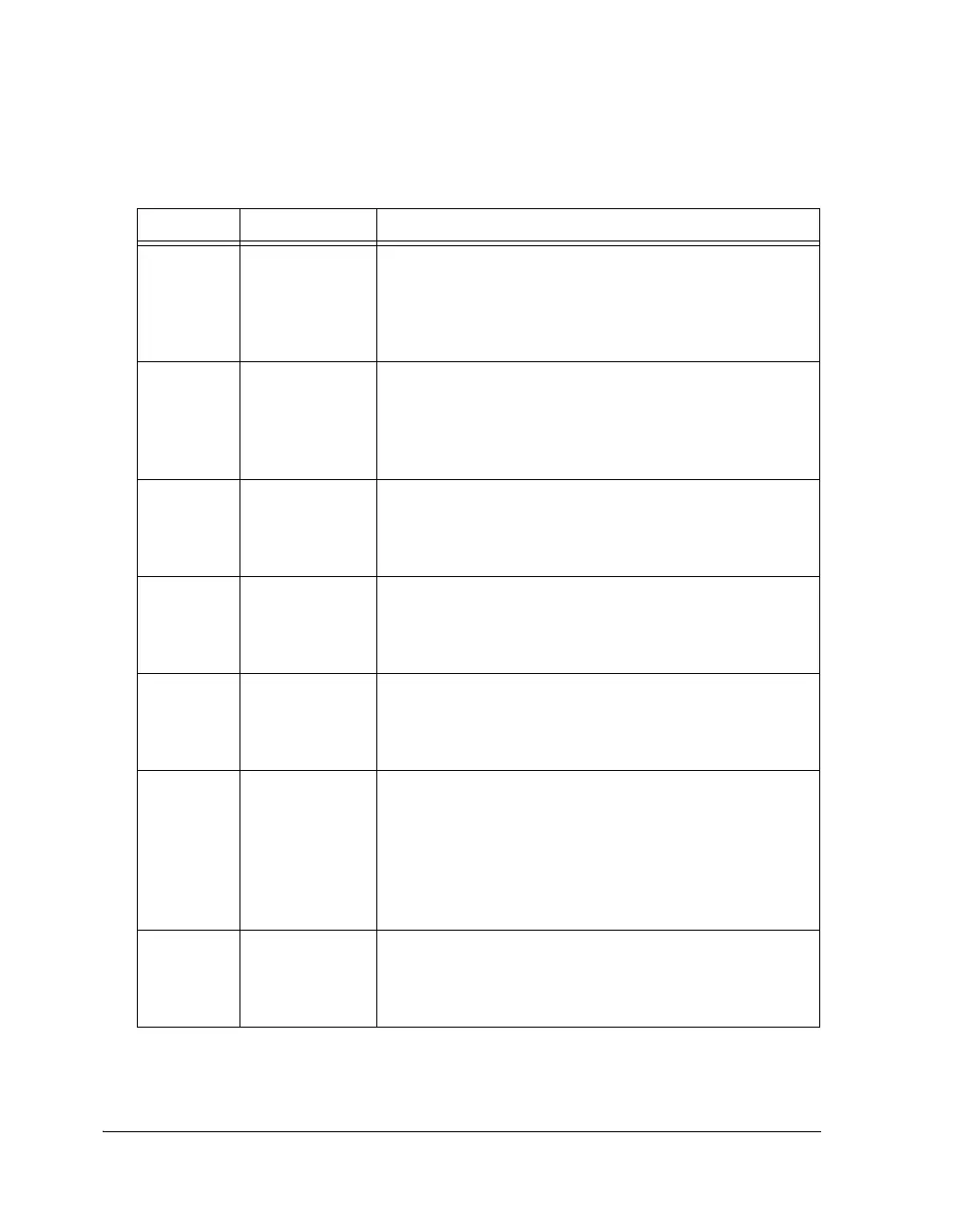

25 SRCOFF SRC Off.

0 = SRC, SPDIF, SRU, PCG, DAI, IDP, PDAP blocks in nor-

mal mode

1 = Turn OFF clock to SRC, SPDIF, SRU, PCG, DAI, IDP,

PDAP

26 PPPDN External Port Enable/Disable. Shuts down the clock to the

asynchronous memory interface as well as SDRAM.

0 = Port is in normal mode

1 = Shut down clock to external port

Reset value = 0

27 SP01OFF SPORT0, 1 Enable/Disable.

0 = SPORTs 0–1 are in normal mode

1 = Shut down clock to SPORTs 0–1

Reset value = 0

28 SP23OFF SPORT2, 3 Enable/Disable.

0 = SPORTs 2–3 are in normal mode

1 = Shut down clock to SPORTs 2–3

Reset value = 0

29 SP45OFF SPORT4, 5 Enable/Disable.

0 = SPORTs 4–5 are in normal mode

1 = Shut down clock to SPORTs 4–5

Reset value = 0

30 SPIOFF SPI Enable/Disable.

0 = SPI is in normal mode

1 = Shut down clock to SPI

Note: When this bit is set (= 1), the FLAGx pins cannot be

used (via the FLAGS7–0 register bits) because the FLAGx

pins are synchronized with the clock.

Reset value = 0

31 TMEROFF Timer Enable/Disable.

0 = Timer is in normal mode

1 = Shutdown clock to Timer

Reset value = 0

Table A-70. PMCTL Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...