ADSP-21368 SHARC Processor Hardware Reference A-173

Register Reference

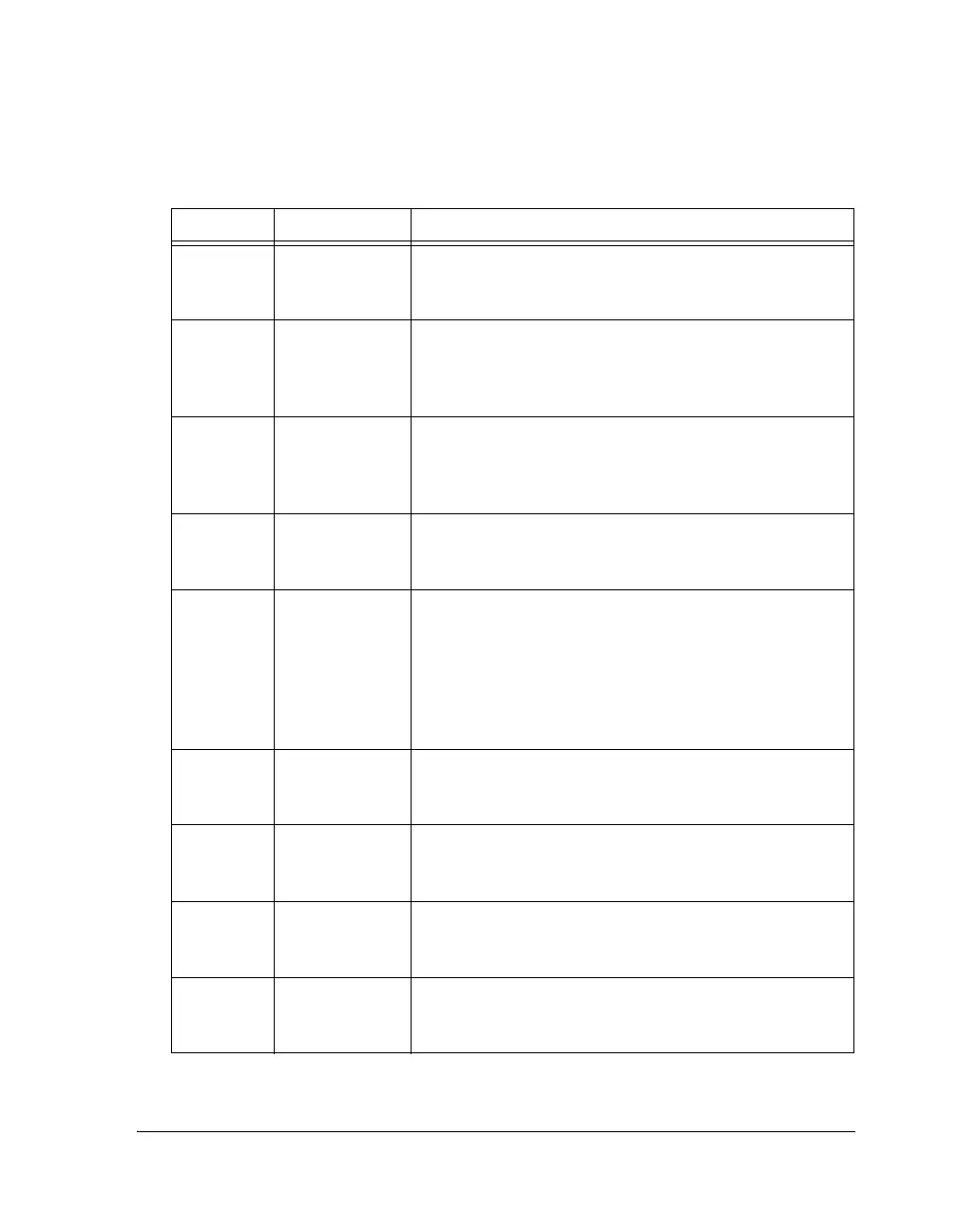

14 UART1OFF UART1 Clock Enable.

0 = UART1 is in normal mode

1 = Shut down clock to UART1

15 PLLBP PLL Bypass Mode Indication.

0 = PLL is in normal mode

1 = Put PLL in bypass mode

Reset value = 0

16 CRAT0 PLL Clock Ratio, CLKIN to CK (read only). Read only. For

more detail, see the PLLM and PLLDx bit descriptions in this

table.

Reset value = CLK_CFG[1:0]

17 CRAT1 PLL Clock Ratio, CLKIN to CK (read only). For more

detail, see the PLLM and PLLDx bit descriptions in this table.

Reset value = CLK_CFG[1:0]

20–18 SDCKR SDCLK Ratio. Core clock to SDRAM clock.

000 = RATIO = 2

001 = RATIO = 2.5

010 = RATIO = 3.0

011 = RATIO = 3.5

100 = RATIO = 4.0

101, 110, 111 = Reserved

21 TWIOFF TWI Clock Enable.

0 = TWI is in normal mode

1 = Shut down clock to TWI

22 SDRAMOFF SDRAM Clock Enable.

0 = SDRAM is in normal mode

1 = Shut down clock to SDRAM

23 PWMOFF PWM Clock Enable.

0 = PWM is in normal mode

1 = Shut down clock to PWM

24 DTCPOFF DTCP Clock Enable.

0 = DTCP is in normal mode

1 = Shut down clock to DTCP

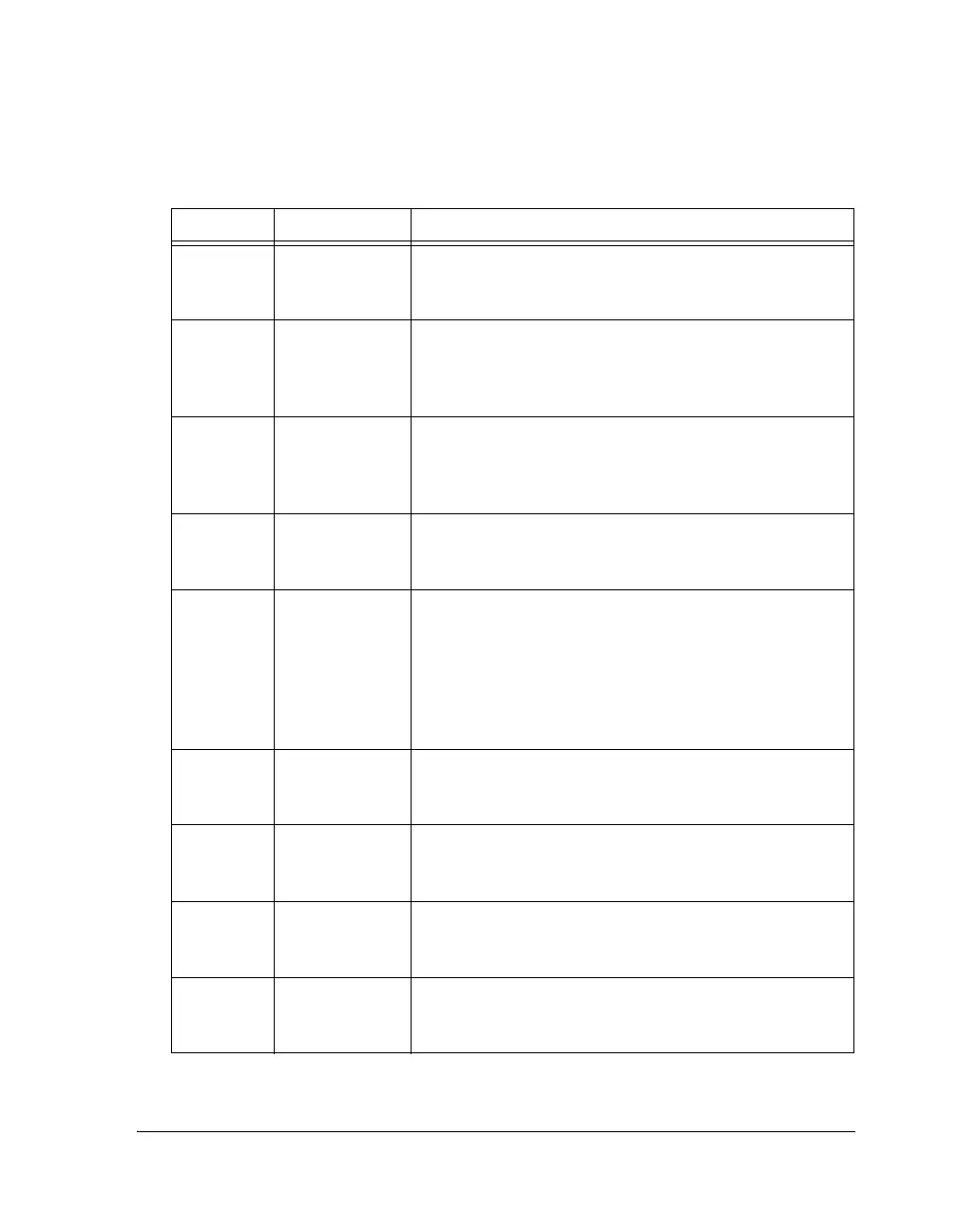

Table A-70. PMCTL Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...