Hardware Breakpoint Control Register

A-176 ADSP-21368 SHARC Processor Hardware Reference

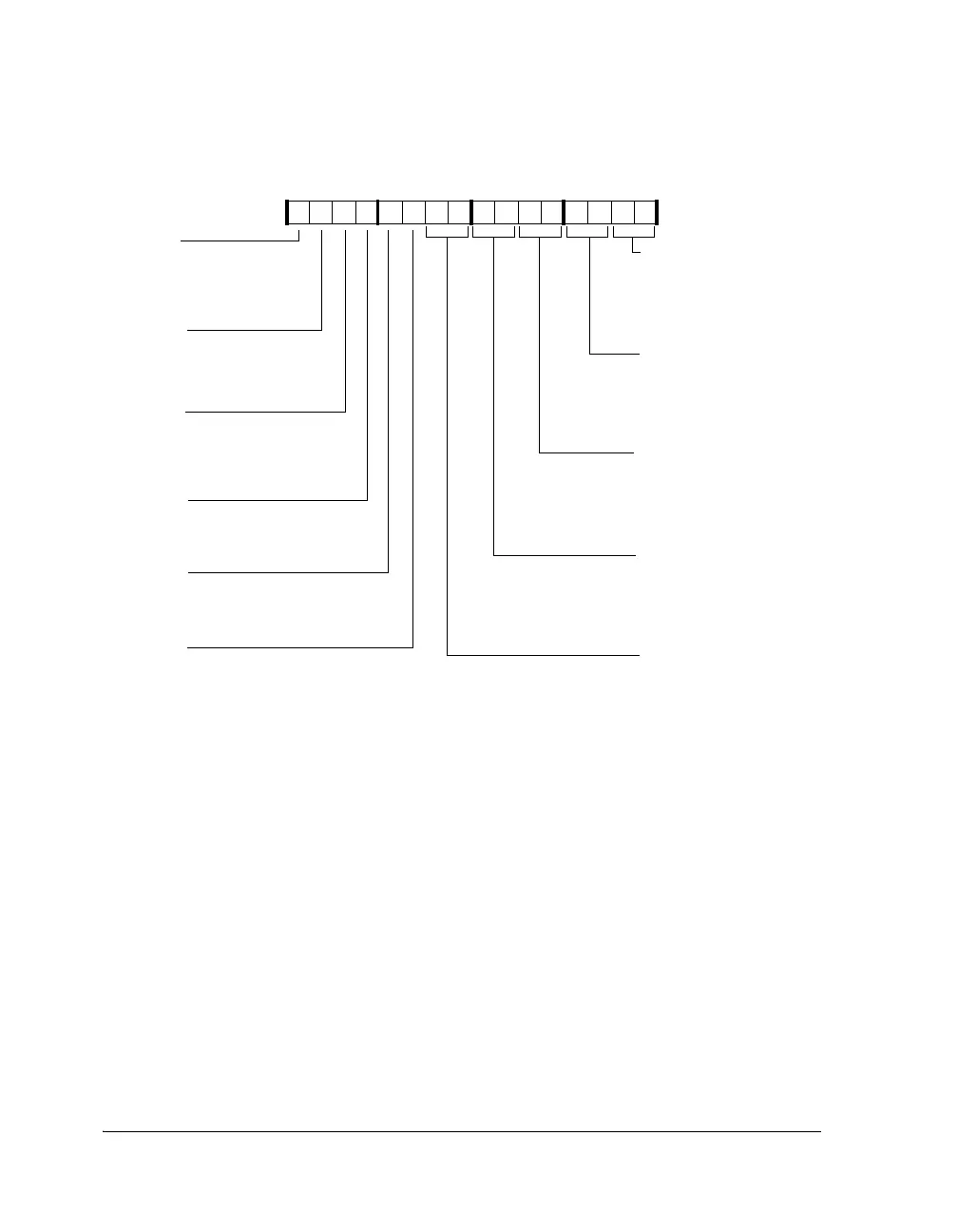

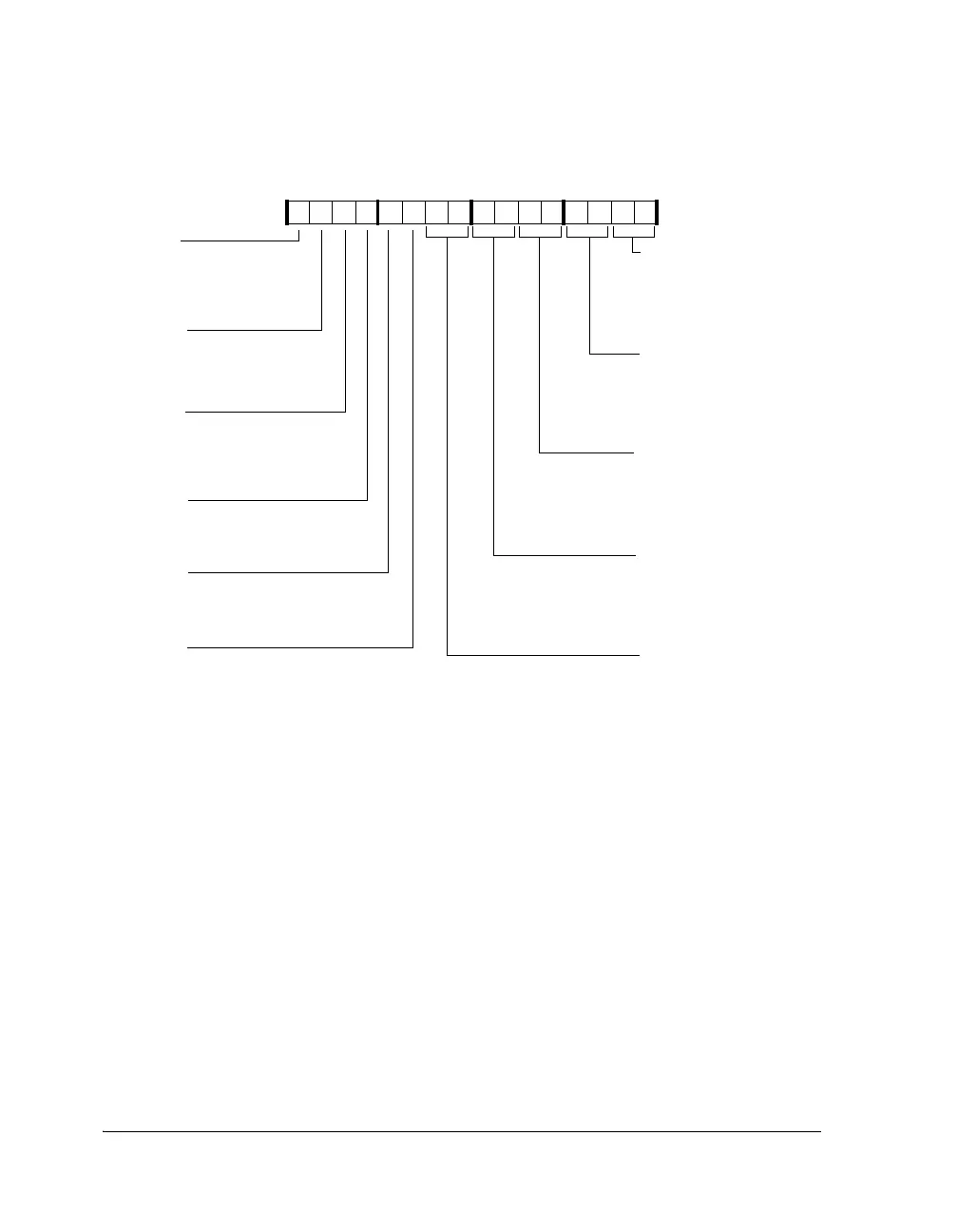

Figure A-85. BRKCTL Register (Bits 0–15)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

1000000000000000

NEGIA3

Negate Instruction Address

Breakpoint #3

1=Enable breakpoint

0=Disable breakpoint

PA1MODE

PA1 Triggering Mode

00=Breakpoint disabled

01=WRITE access

10=READ access

11=Any access

NEGIA2

Negate Instruction Address

Breakpoint #2

1=Enable breakpoint

0=Disable breakpoint

NEGIA1

Negate Instruction Address

Breakpoint #1

1=Enable breakpoint

0=Disable breakpoint

NEGDA2

Negate DM Address Breakpoint #2

1=Enable breakpoint

0=Disable breakpoint

NEGDA1

Negate DM Address Breakpoint #1

1=Enable breakpoint

0=Disable breakpoint

DA1MODE

DA1 Triggering Mode

00=Breakpoint disabled

01=WRITE access

10=READ access

11=Any access

DA2MODE

DA2 Triggering Mode

00=Breakpoint disabled

01=WRITE access

10=READ access

11=Any access

IO1MODE

IO1 Triggering Mode

00=Breakpoint disabled

01=WRITE access

10=READ access

11=Any access

EP1MODE

EP1 Triggering Mode

00=Breakpoint disabled

01=WRITE access

10=READ access

11=Any access

NEGPA1

Negate PM Address Breakpoint #1

1=Enable breakpoint

0=Disable breakpoint

BRKCTL (0x30025)

(Bits 15-0)

Loading...

Loading...