ADSP-21368 SHARC Processor Hardware Reference A-67

Register Reference

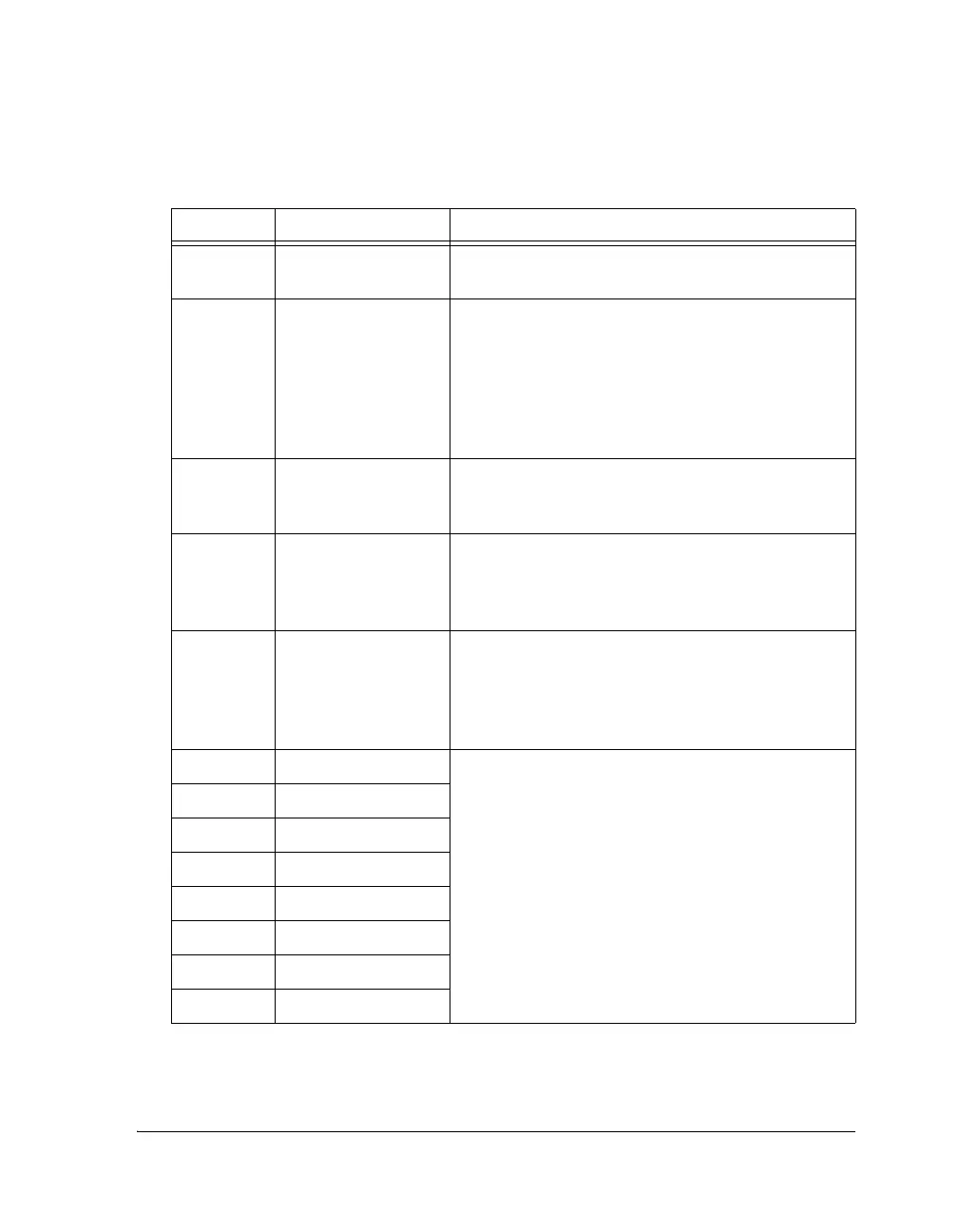

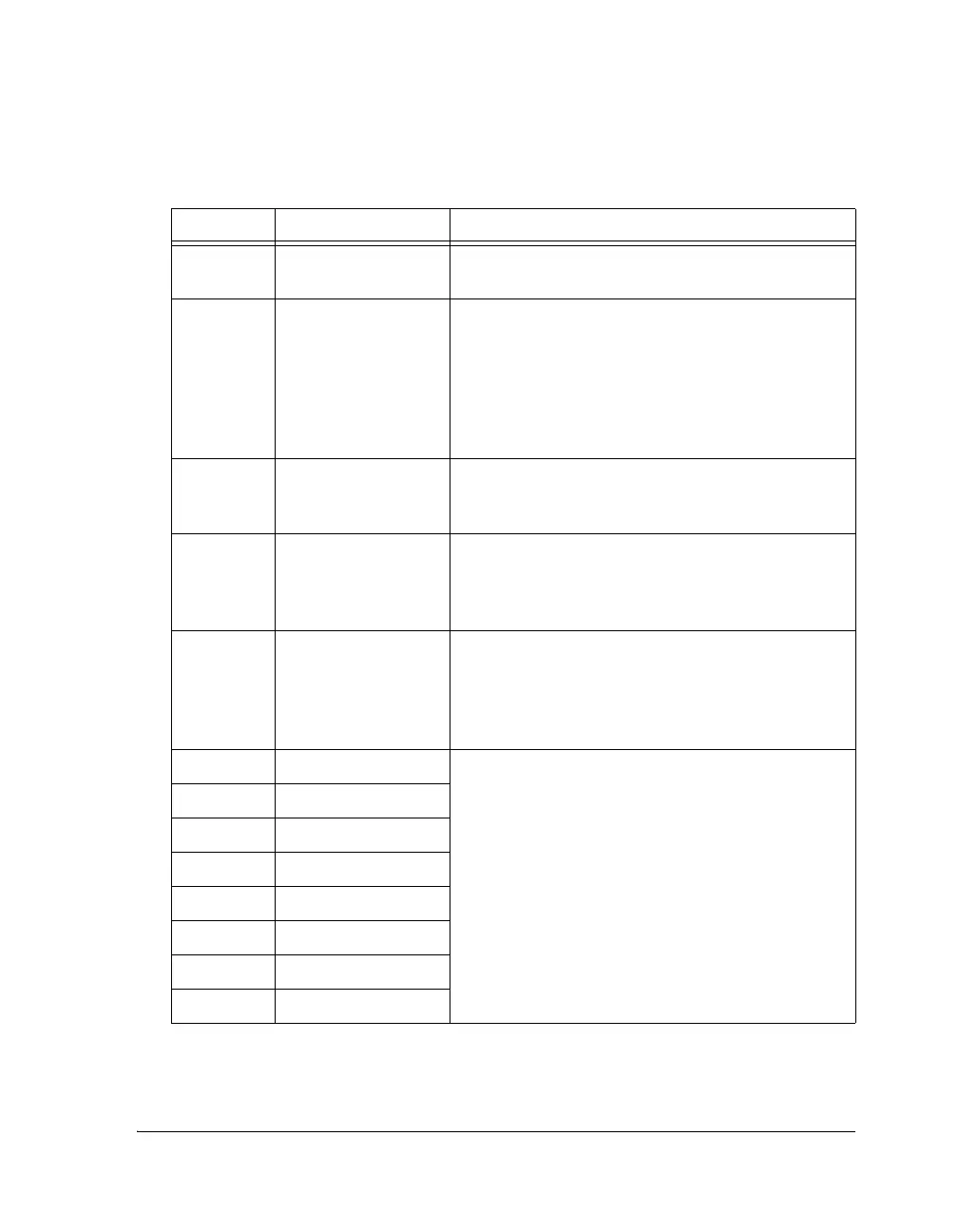

Table A-16. IDP_CTL0 Register Bit Descriptions

Bit Name Description

3–0 IDP_NSET Monitors number of FIFO entries where N > samples

raises interrupt controller bit 8.

4IDP_BHD IDP Buffer Hang Disable. Reads of an empty FIFO or

writes to a full FIFO make the core hang. This condi-

tion continues until the FIFO has valid data (in the case

of reads) or the FIFO has at least one empty location (in

the case of writes).

0 = Core hang is enabled

1 = Core hang is disabled

5 IDP_DMA_EN DMA Enable. Enables DMA on all IDP channels.

0 = DMA not enabled

1 = DMA enabled

6IDP_CLROVRFIFO Overflow Clear Bit. Writes of 1 to this bit clear

the overflow condition in the DAI_STAT register.

Because this is a write-only bit, it always returns LOW

when read.

7IDP_ENABLEEnable IDP. 1 to 0 transition on this bit clears

IDP_FIFO.

0 = IDP is disabled. Data does not come to IDP_FIFO

from IDP channels.

1 = IDP is enabled.

10–8 IDP_SMODE0 Serial Input Mode Select. These eight inputs (0-7), each

of which contains 3 bits, indicate the mode of the serial

input for each of the eight IDP channels.

Input format:

000 = Left-justified sample pair mode

001 = I

2

S mode

010 = Left-justified 32 bits

011 = I

2

S 32 bits

100 = Right-justified 24 bits

101 = Right-justified 20 bits

110 = Right-justified 18 bits

111 = Right-justified 16 bits

13–11 IDP_SMODE1

16–14 IDP_SMODE2

19–17 IDP_SMODE3

22–20 IDP_SMODE4

25–23 IDP_SMODE5

28–26 IDP_SMODE6

31–29 IDP_SMODE7

Loading...

Loading...