ADSP-21368 SHARC Processor Hardware Reference A-93

Register Reference

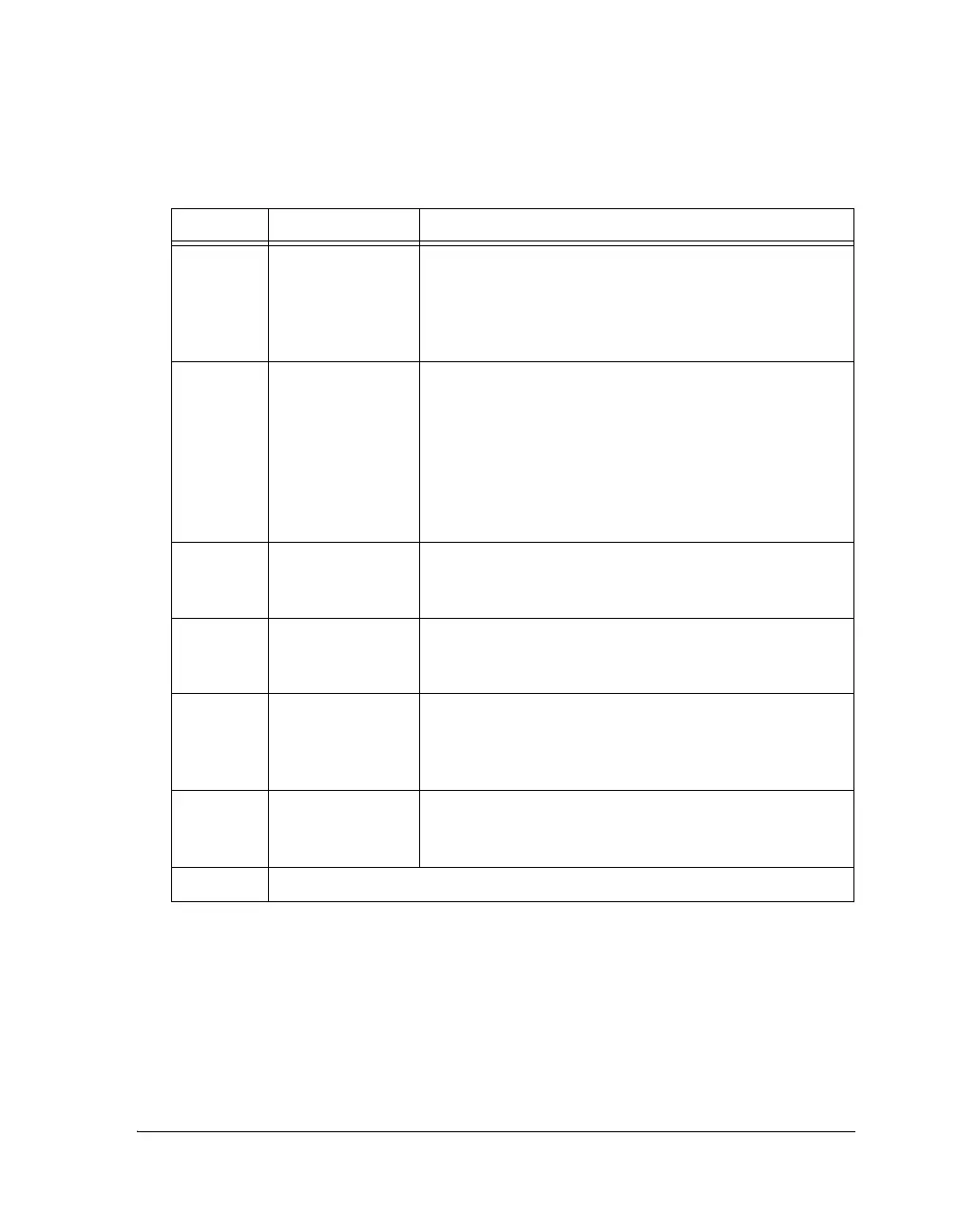

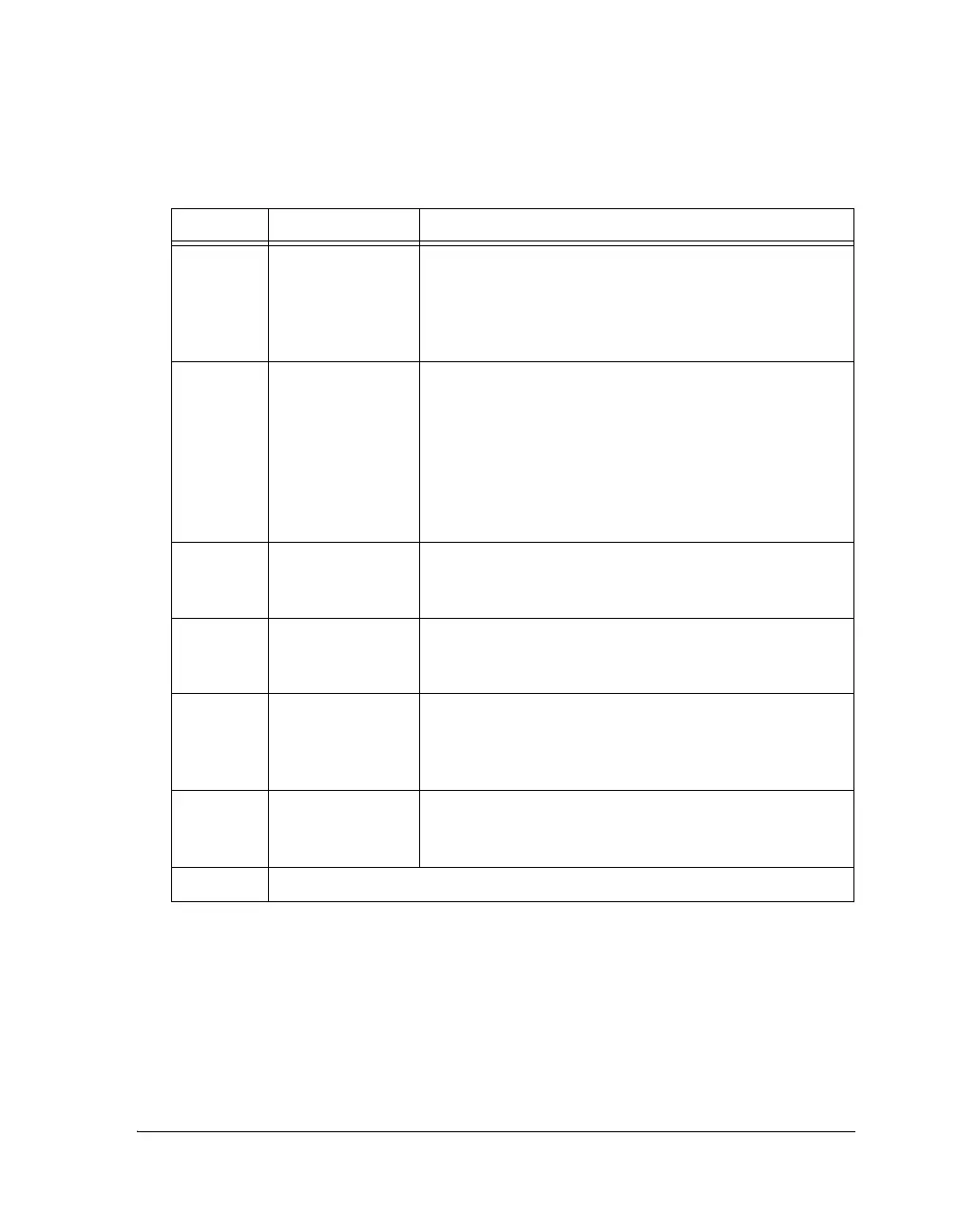

Table A-38. DIRCTL Register Bit Descriptions

Bit Name Description

1–0 DIR_BIPHASE Parity Biphase Error Control.

00 = No action taken

01 = Hold last valid sample

10 = Replace invalid sample with zeros

11 = Reserved

3–2 DIR_LOCK Lock Error Control.

00 = No action taken

01 = Hold last valid sample

10 = Send zeros after the last valid sample

11 = Soft mute of the last valid audio sample is performed as

if NOSTREAM is asserted. This is valid only when linear

PCM audio data is in the stream. With non-linear audio

data, this mode defaults to LOCKERROR_CTL = 10.

4DIR_SCDF_LRSingle-Channel, Double-Frequency Channel Select.

0 = Left channel

1 = Right channel

5DIR_SCDFSingle-Channel, Double-Frequency Mode Enable.

0 = 2 channel mode disabled

1 = 2 channel mode enabled

6DIR_MUTEMute.

0 = Mute disabled

1 = Mute serial data outputs, maintaining clocks (digital

black)

7DIR_PLLDISDisable PLL. Determines clock input.

0 = Use derived clock from the digital PLL

1 = Use clock input from external PLL

31–8 Reserved

Loading...

Loading...