DAI/DPI Registers

A-110 ADSP-21368 SHARC Processor Hardware Reference

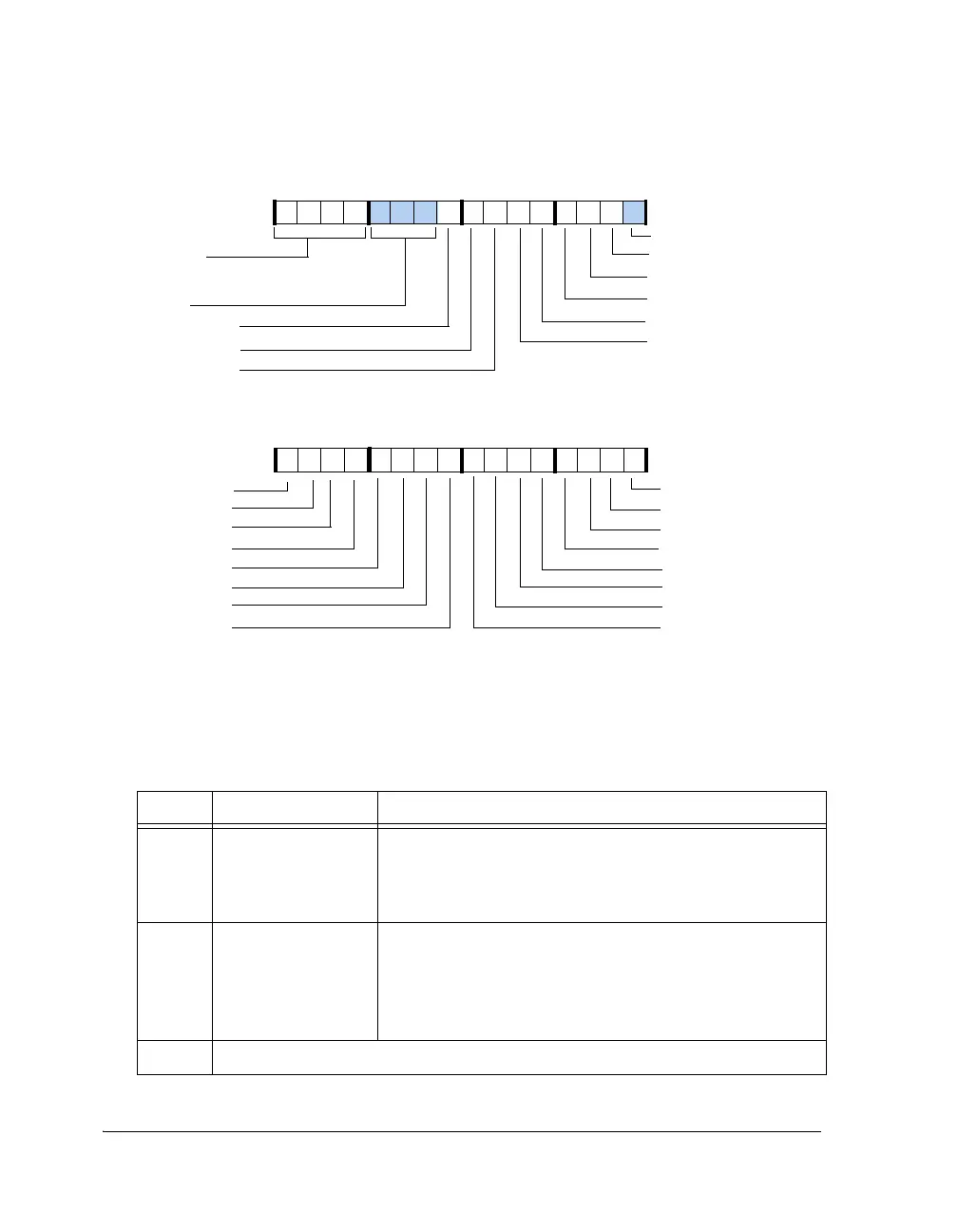

Figure A-41. DAI_STAT Register

Table A-45. DAI_STAT Register Bit Descriptions

Bit Name Description

7–0 SRU_PINGx_STAT Ping-pong DMA Status (Channel). Indicates the status of

ping-pong DMA in each respective channel (channel 0–7).

0 = DMA is not active

1 = DMA is active

15–8 SRU_OVFx Sticky Overflow Status (Channel). Provides overflow status

information for each channel (bit 8 for channel 0 through bit

15 for channel 7).

0 = No overflow

1 = Overflow has occurred

16 Reserved

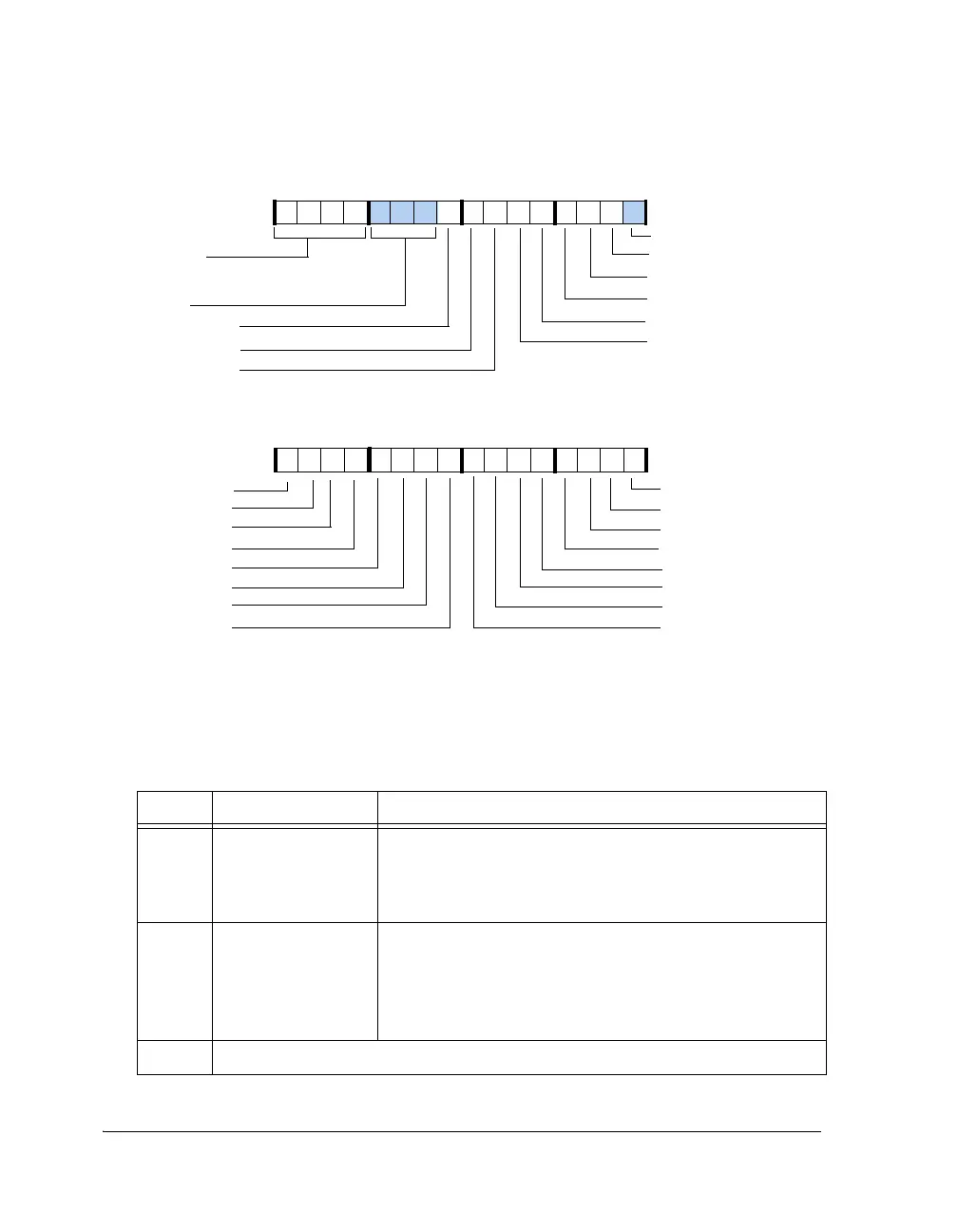

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000000000000000

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

IDP_FIFOSZ

Reserved

Number of Valid Data in IDP FIFO

IDP_DMA7_STAT

IDP_DMA6_STAT

IDP_DMA3_STAT

IDP_DMA4_STAT

IDP_DMA1_STAT

IDP_DMA2_STAT

IDP_DMA0_STAT

IDP_DMA5_STAT

SRU_PING1_STAT

SRU_OVF0

DAI_STAT (0x24B8)

SRU_PING0_STAT

SRU_PING2_STAT

SRU_PING3_STAT

SRU_PING4_STAT

SRU_PING5_STAT

SRU_PING6_STAT

SRU_PING7_STAT

SRU_OVF1

SRU_OVF2

SRU_OVF4

SRU_OVF7

SRU_OVF6

SRU_OVF5

SRU_OVF3

Reserved

IDP Channel Overflow (Sticky) Ping-Pong DMA Chan-

nel Status

DMA Active Status for

IDP Channel

Loading...

Loading...