Two Wire Interface Registers

A-134 ADSP-21368 SHARC Processor Hardware Reference

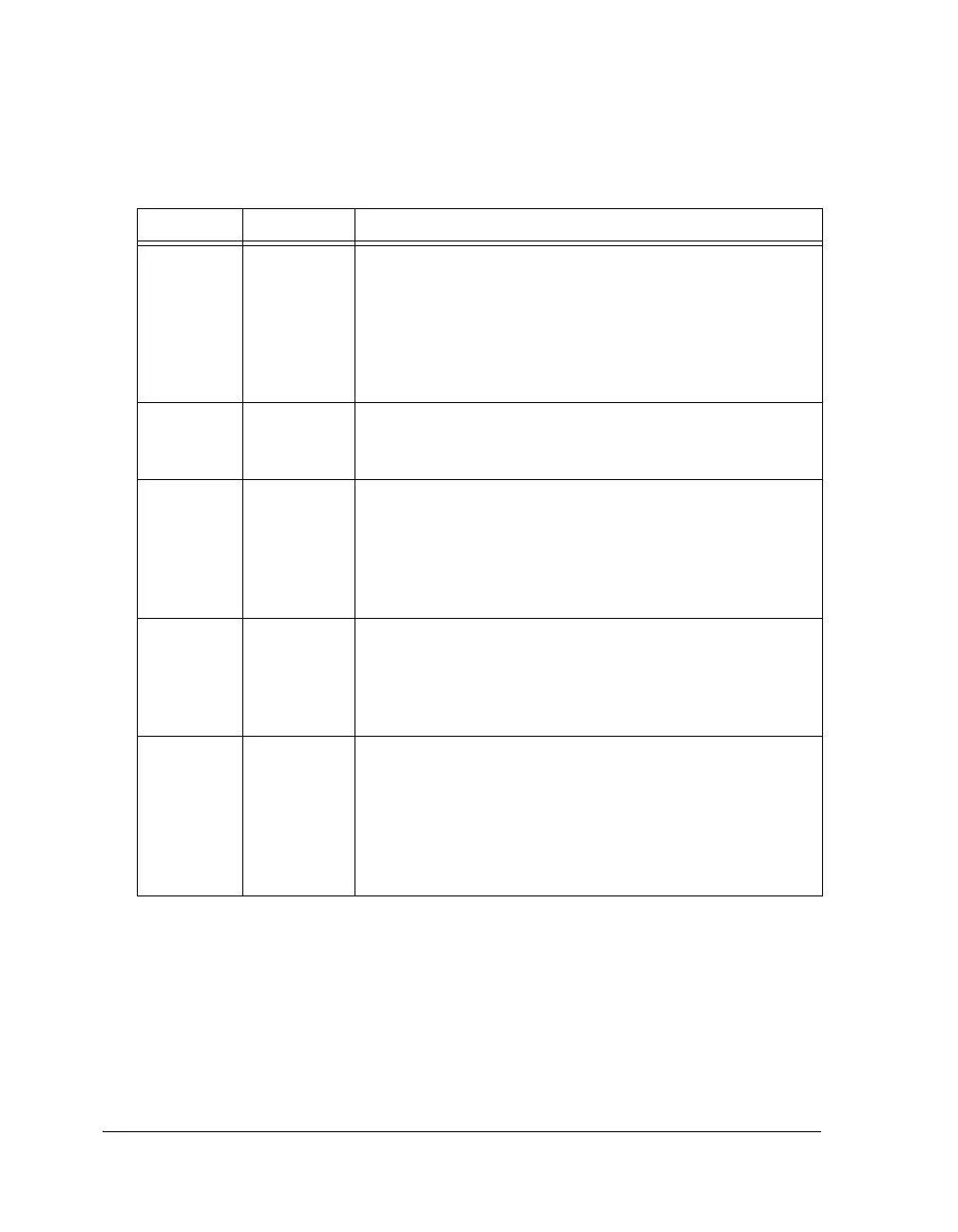

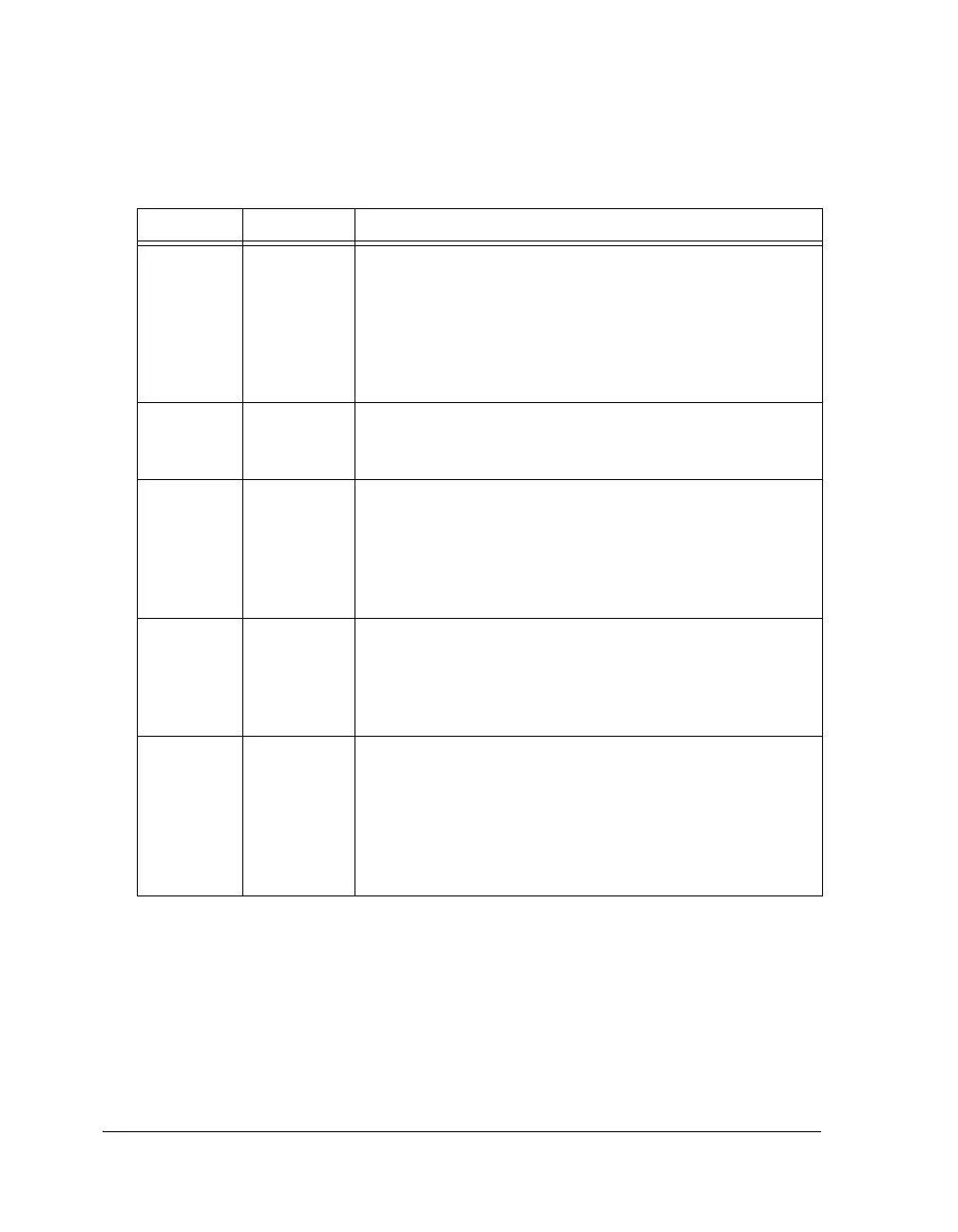

Table A-56. Slave Mode Control Register Bit Descriptions

Bit Name Description

0 TWISEN Slave Enable.

0 = The slave is not enabled. No attempt is made to identify a

valid address. If cleared during a valid transfer, clock stretching

ceases, the serial data line is released and the current byte is not

acknowledged.

1 = The slave is enabled. Enabling slave and master modes of

operation concurrently is allowed.

1 TWISLEN Slave Address Length.

0 = Address is a 7-bit address

1= Reserved. Setting this bit to 1 causes unpredictable behavior.

2 TWIDVAL Slave Transmit Data Valid.

0 = Data in the transmit FIFO is for master mode transmits and

is not allowed to be used during a slave transmit, and the transmit

FIFO is treated as if it is empty.

1 = Data in the transmit FIFO is available for a slave transmis-

sion.

3 TWINAK Not Acknowledged.

0 = Slave receive transfer generates an ACK at the conclusion of a

data transfer.

1 = Slave receive transfer generates a data NAK at the conclusion

of a data transfer. The slave is still considered to be addressed.

4 TWIGCE General Call Enable. General call address detection is available

only when slave mode is enabled.

0 = General call address matching is not enabled

1 = General call address matching is enabled. Regardless of the

selected address length of slave address, a general call slave receive

transfer is accepted. All status and interrupt source bits associated

with transfers are updated.

Loading...

Loading...