Interrupt Vector Tables

B-2 ADSP-21368 SHARC Processor Hardware Reference

Note that the SPI has only one interrupt for both transmit and receive

operations and each serial port (SPORT) has only one interrupt for both

transmit and receive.

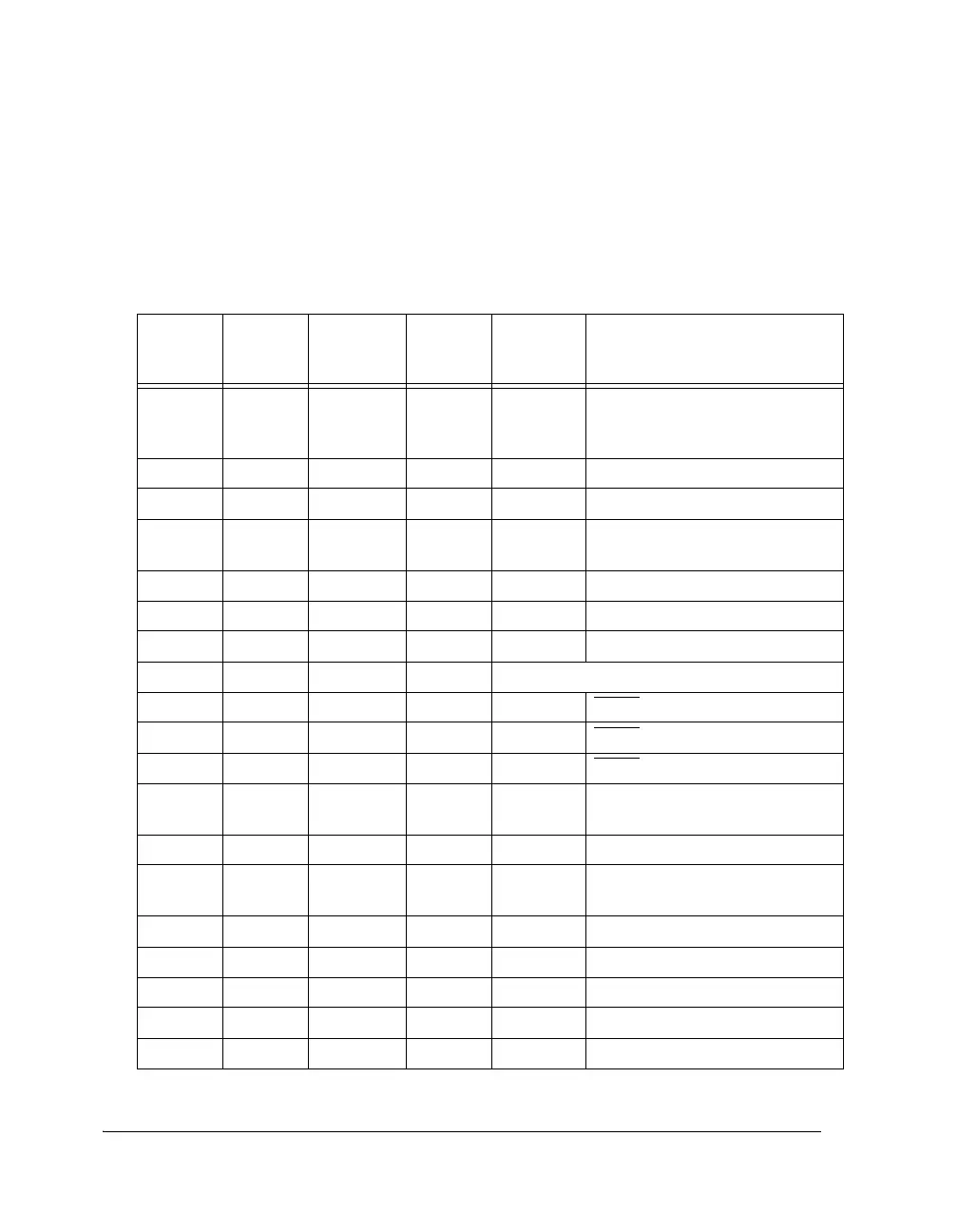

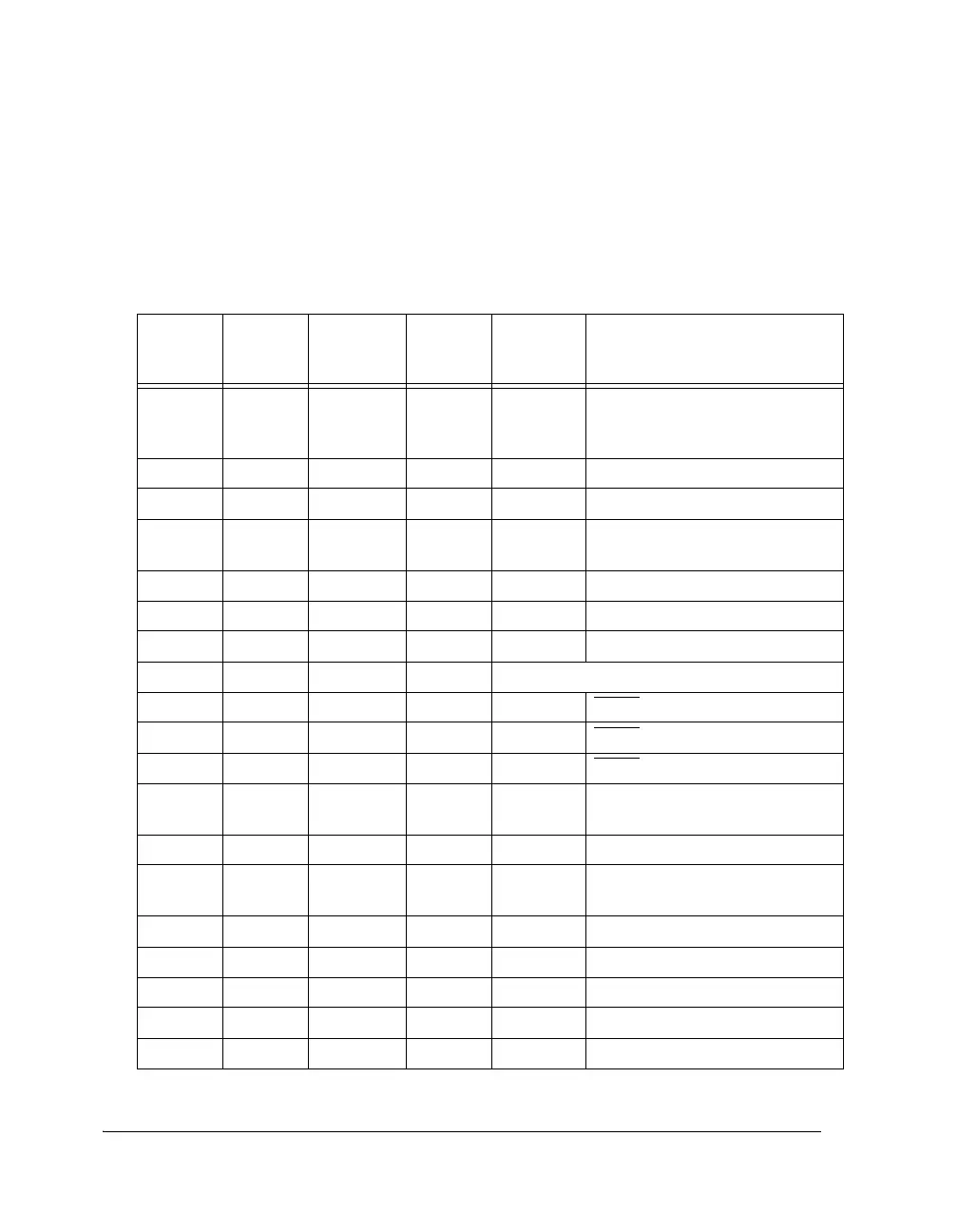

Table B-2. Interrupt Vector Addresses

Interrupt

Number

Register IRPTL/

LIRPTL/

MASK Bit#

Vector

Address

Interrupt

Name

Function

0 IRPTL 0 0x00 EMUI Emulator (read-only,

non-maskable)

HIGHEST PRIORITY

1 IRPTL 1 0x04 RSTI

1

Reset (read-only non-maskable)

2 IRPTL 2 0x08 IICDI Illegal input condition detected

3 IRPTL 3 0x0C SOVFI Status loop or mode stack over-

flow; or PC stack full

4 IRPTL 4 0x10 TMZHI Timer=0 (high priority option)

5 IRPTL 5 0x14 SPERRI SP error interrupt

6 IRPTL 6 0x18 BKPI Hardware breakpoint interrupt

7 IRPTL 7 0x1C Reserved

8IRPTL8 0x20IRQ2I IRQ2I

asserted

9IRPTL9 0x24IRQ1I IRQ1I asserted

10 IRPTL 10 0x28 IRQ0I IRQ0I asserted

11 IRPTL 11 0x2C P0I Programmable interrupt 0

(DAI1)

12 IRPTL 12 0x30 P1I

2

Programmable interrupt 1 (SPIA)

13 IRPTL 13 0x34 P2I Programmable interrupt 2

(GPTMR0)

14 IRPTL 14 0x38 P3I Programmable interrupt 3 (SP1)

15 IRPTL 15 0x3C P4I Programmable interrupt 4 (SP3)

16 IRPTL 16 0x40 P5I Programmable interrupt 5 (SP5)

17 LIRPTL 0 0x44 P6I Programmable interrupt 6 (SP0)

18 LIRPTL 1 0x48 P7I Programmable interrupt 7 (SP2)

Loading...

Loading...