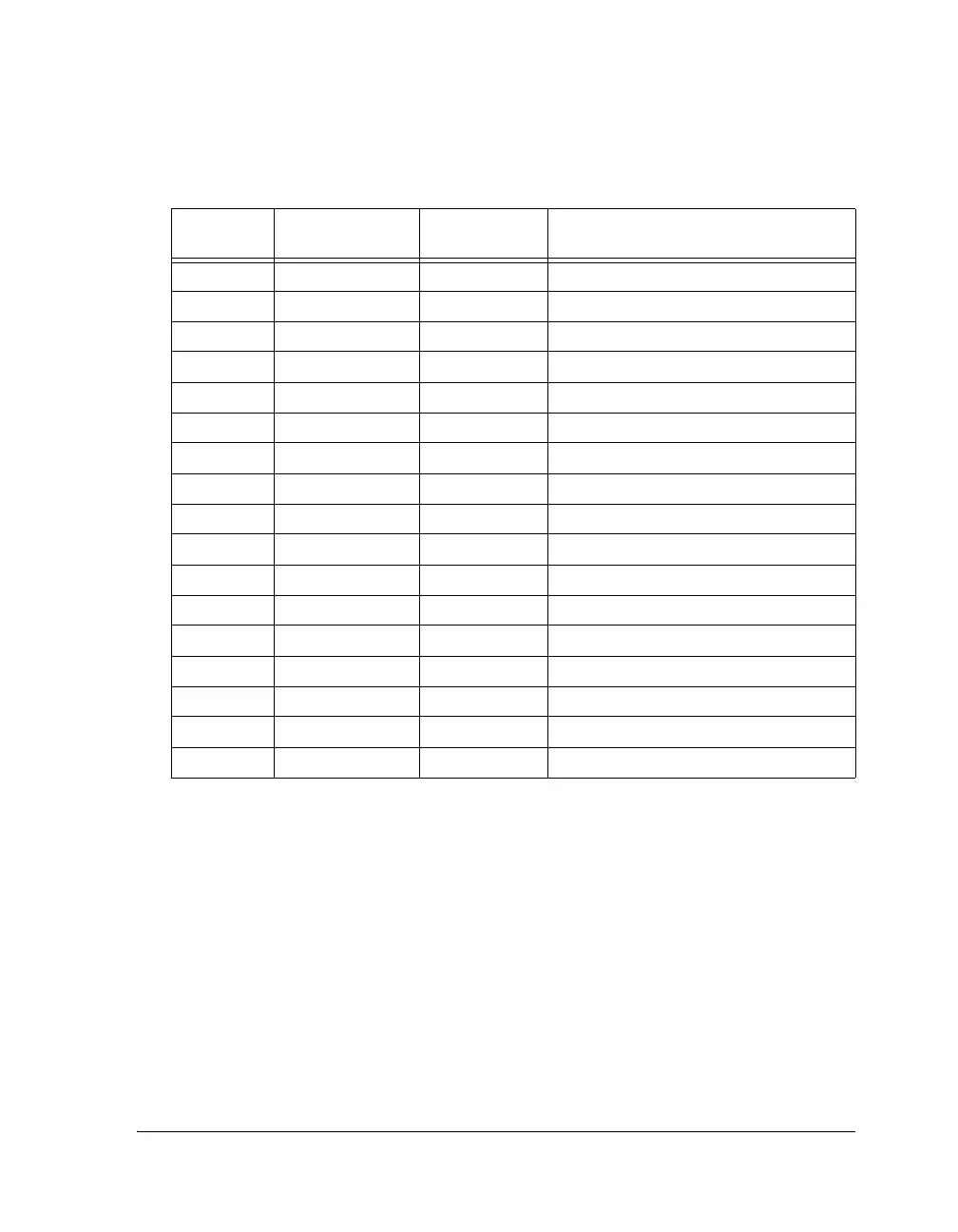

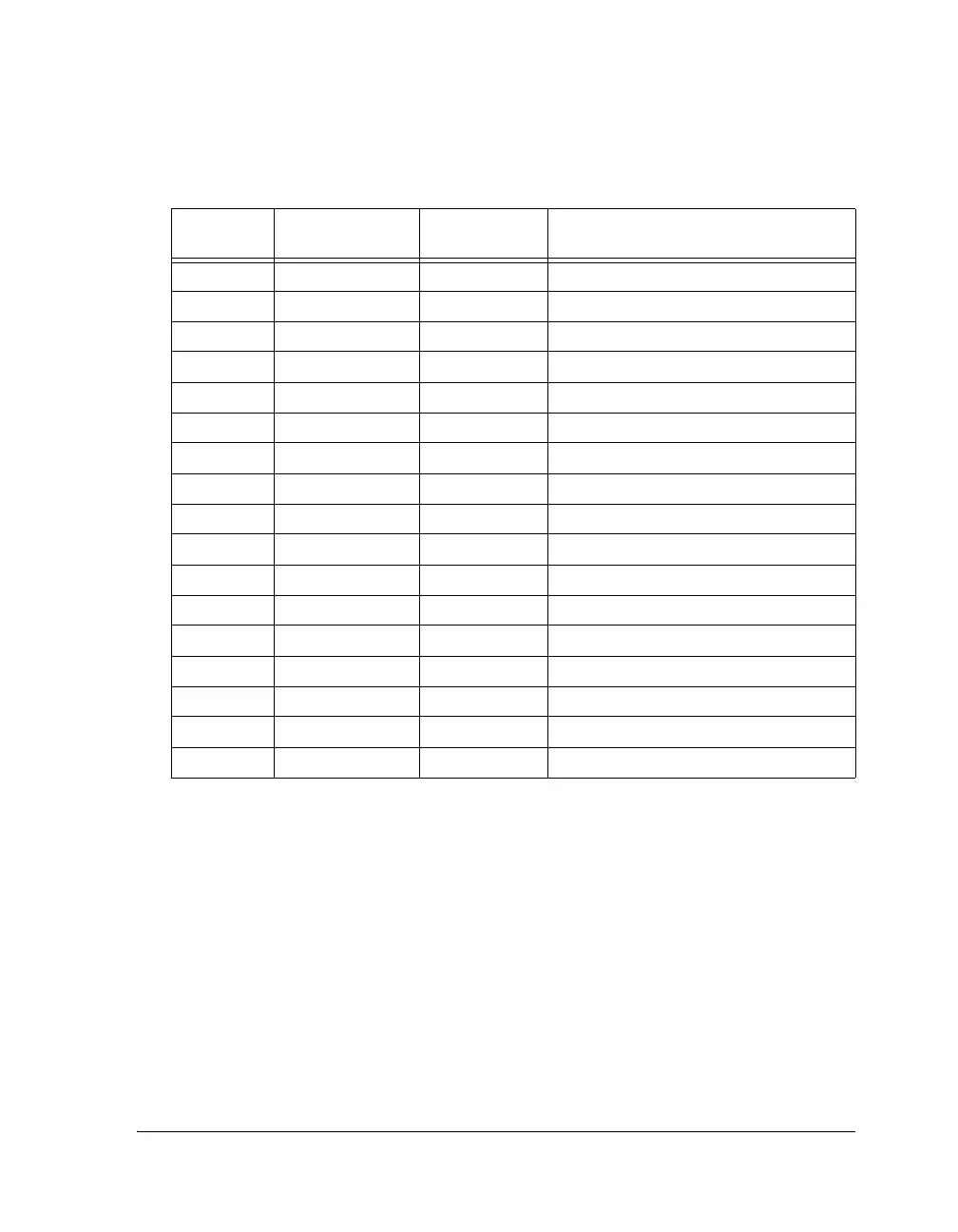

ADSP-21368 SHARC Processor Hardware Reference B-5

Interrupts

11 GPTMR1I 0x0A Genera-purpose Timer 1 interrupt

12 SP7I 0x0B Serial port 7 interrupt

13 DAI 0x0C DAI low priority interrupt

14 EP1I 0x0D External port channel 1 interrupt

15 DPI 0x0E DPI interrupt

16 MTMDMAI 0x0F Memory-to-memory DMA interrupt

17 SP6I 0x10 Serial Port 6 interrupt

18 GPTMR2I 0x11 General-purpose timer 2 interrupt

19 SPIBI 0x12 SPI B interrupt

20 UART0RXI 0x13 UART0 RX interrupt

1

21 UART1RXI 0x14 UART1 RX interrupt

1

22 UART0TXI 0x15 UART0 TX interrupt

1

23 UART1TXI 0x16 UART1 TX interrupt

1

24 TWII 0x17 TWI interrupt

1

25 PWMI 0x18 PWM interrupt

1

26 Reserved 0x18–0x1E Reserved

27 LOGIC HIGH 0x1F Software option to set IOP interrupts

1

1 These interrupts are not connected to the processor core interrupts by default. If these interrupts

are required, then the PICR registers should be programmed explicitly. For more information,

see “Peripheral Interrupt Priority Control Registers” in Appendix A, Register Reference.

Table B-3. Interrupt Selection Values (Cont’d)

No Interrupt Source Interrupt Select

Value (5-Bits)

Comments

Loading...

Loading...