ADSP-21368 SHARC Processor Hardware Reference 3-85

External Port

keep these signals from drifting near input receiver thresholds when all

drivers are three-stated. Note that single processor systems with ID = 000

also enable these pull-up devices.

When the bus master stops using the bus, its BRx line is deasserted, allow-

ing other processors to arbitrate for mastership if they need it. If no other

processors are asserting their BRx line when the master deasserts its BRx,

the master retains control of the bus and continues to drive the memory

control signals until: 1) it needs to use the bus again, or 2) another proces-

sor asserts its BRx line.

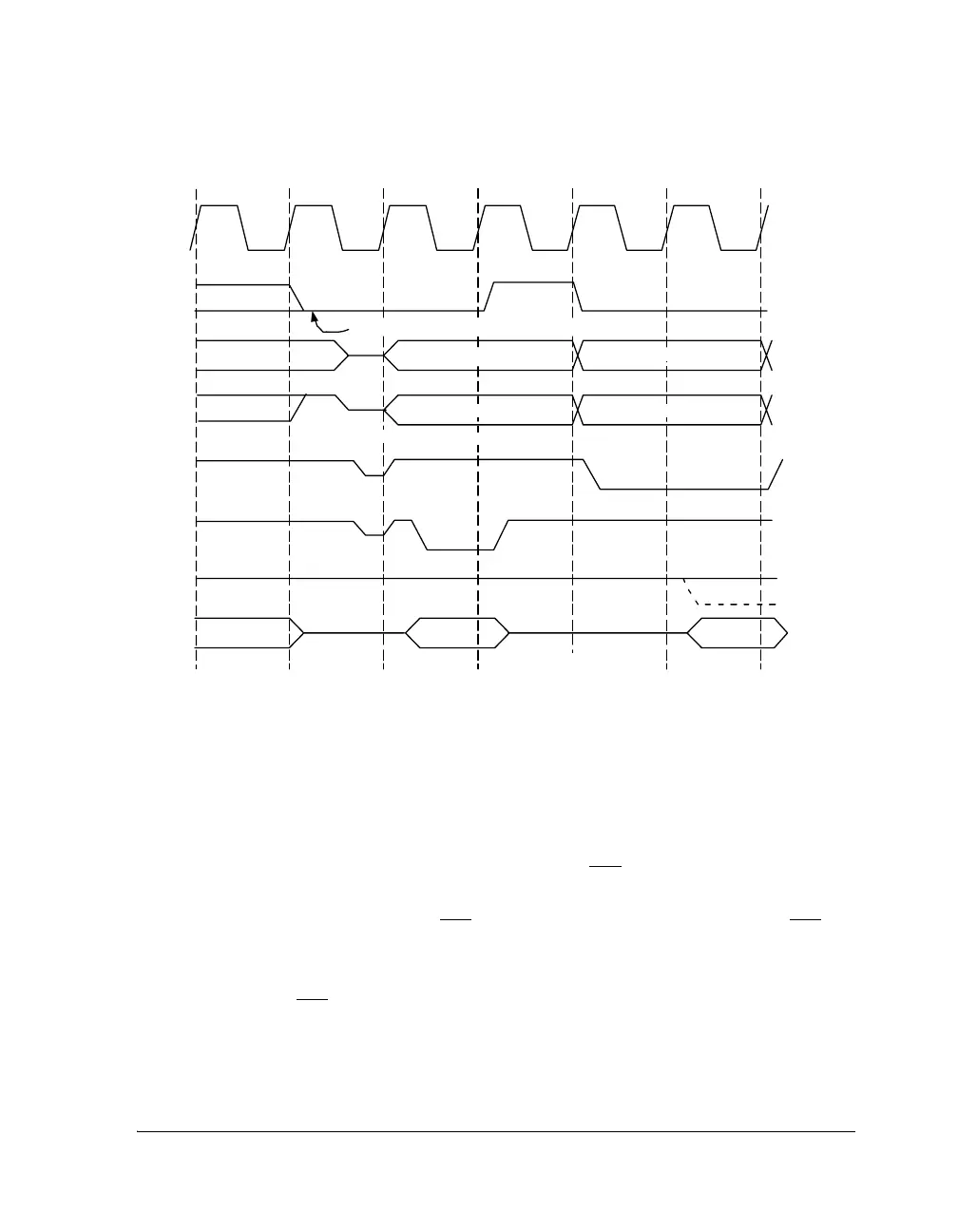

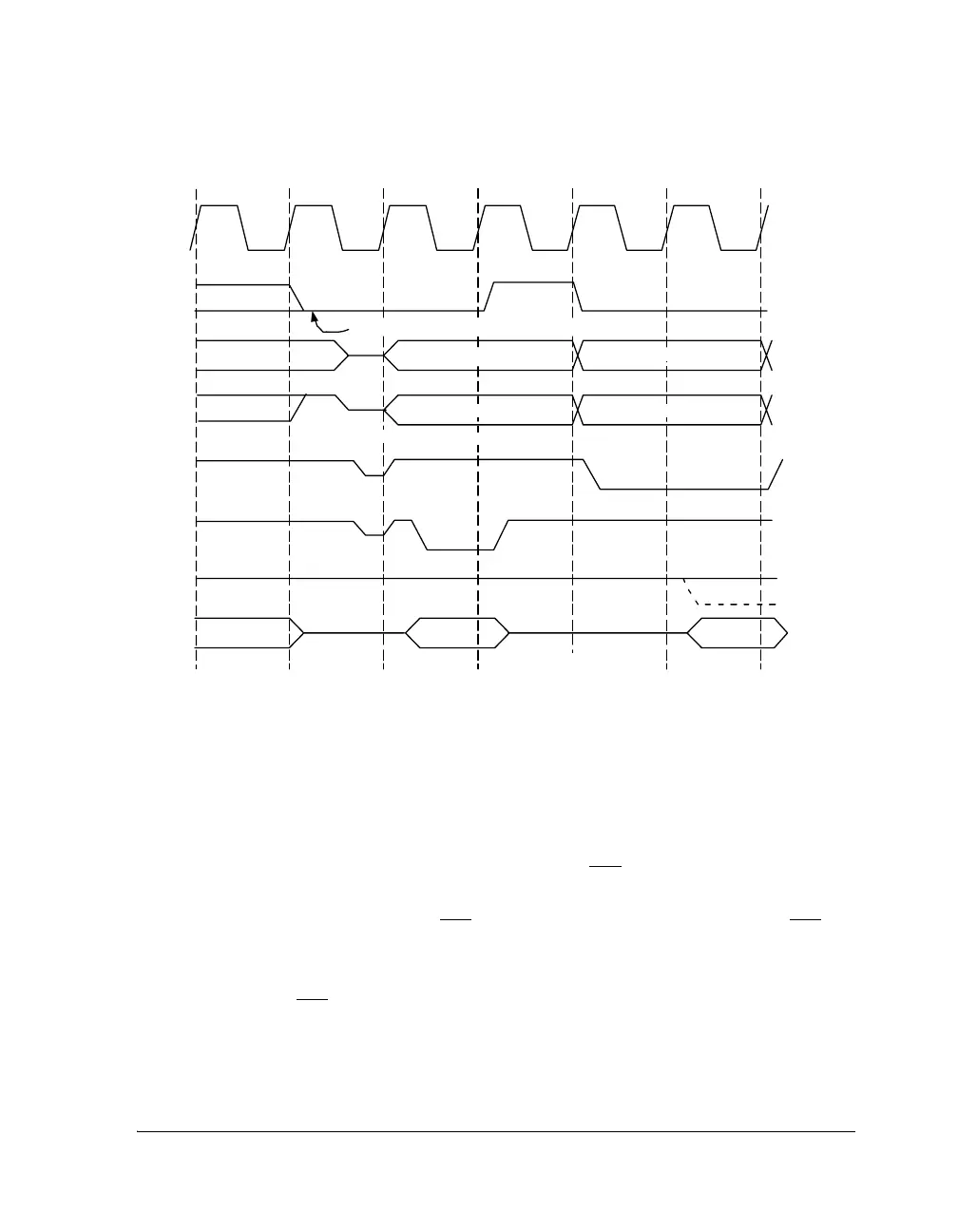

Figure 3-16. Bus Request and Read/Write Timing

BRx

123456

ADDR

MSx

RD

WR

ACK

DATA

BTC

VALID

OPTIONAL

VALID

BTC DOES NOT

OCCURIF NO OTHER

BRS ASSERTED

VALID

VALID

VALID VALID

HI GHEST P RIORITY REQUESTER BECOMES BUS MASTER

MS, S TROBES DRIVEN I NACTIVE BEFORE THREE-STATE

CLKIN

Loading...

Loading...