ADSP-21368 SHARC Processor Hardware Reference 4-57

Digital Audio/Digital Peripheral Interfaces

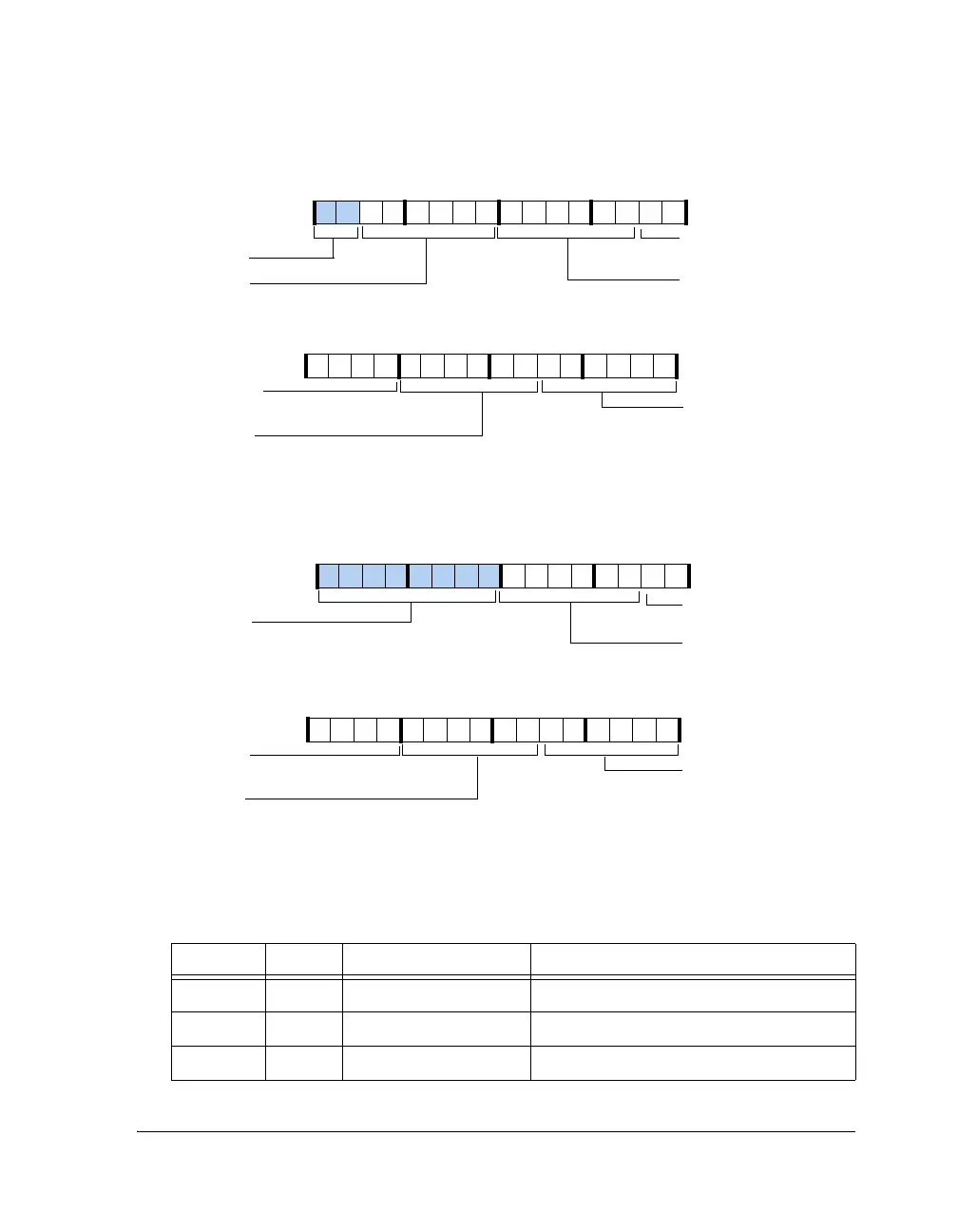

Figure 4-48. SRU2_PIN1 Register

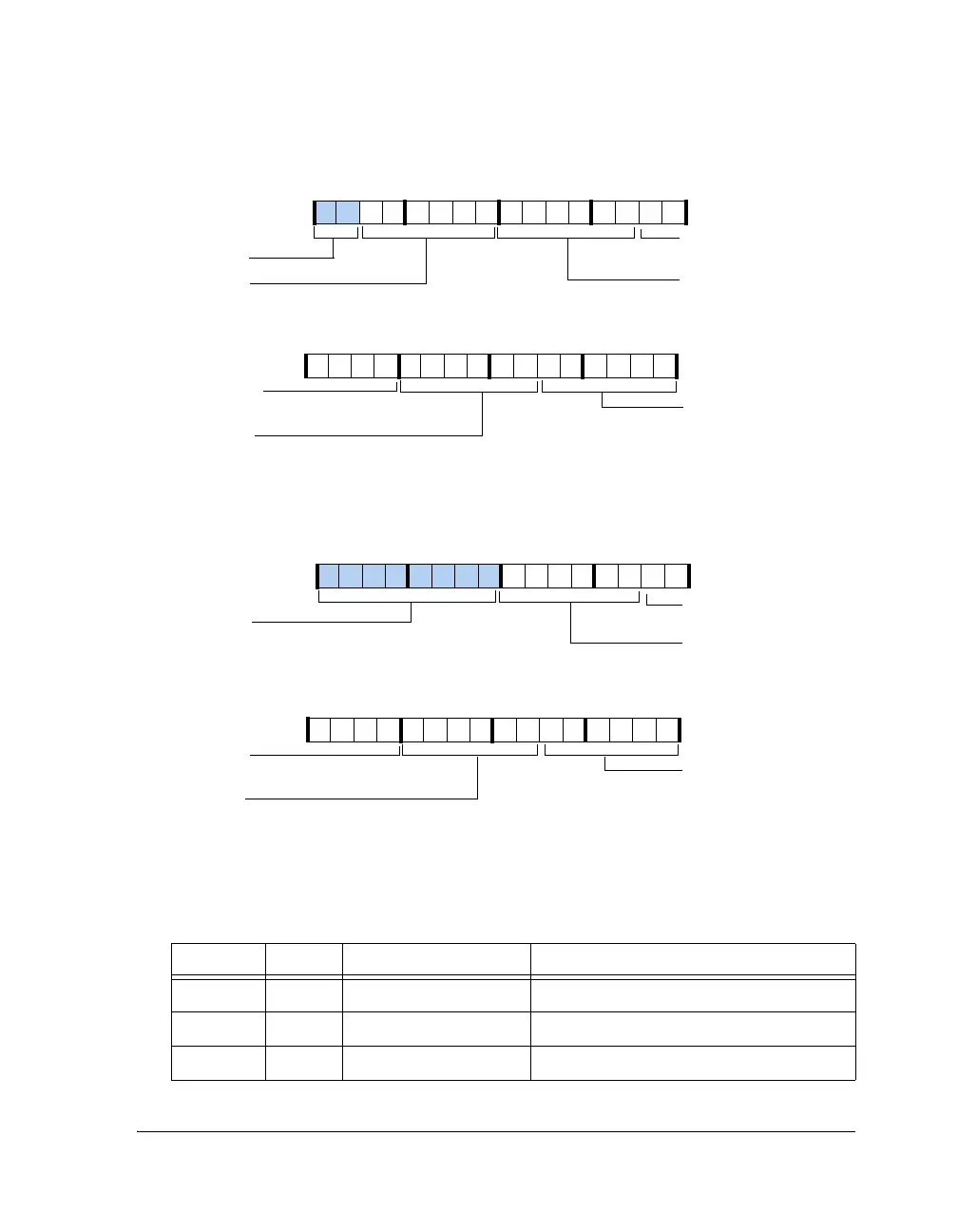

Figure 4-49. SRU2_PIN2 Register

Table 4-12. Group B Signals

Binary Decimal Signal Description

000000 00 LOGIC_LEVEL_LOW Logic level low (0)

000001 01 LOGIC_LEVEL_HIGH Logic level high (1)

000010 02 DPI_P01_O External pin 1

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

1000000000100110

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

1101101101001100

DPI_PB10_I

DPI Pin Buffer 10 Input

DPI_PB08_I

DPI Pin Buffer 8 Input

DPI_PB09_I

DPI Pin Buffer 9 Input

DPI_PB08_I

DPI_PB07_I

DPI Pin Buffer 7 Input

DPI_PB06_I

DPI Pin Buffer 6 Input

SRU2_PIN1

(0x01C11)

DPI Pin Buffer 8 Input

Reset = 0x002DB699

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

1000000000100010

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

DPI_PB13_I

DPI Pin Buffer 13 Input

DPI_PB14_I

DPI Pin Buffer 14 Input

DPI_PB13_I

DPI_PB12_I

DPI Pin Buffer 12 Input

DPI_PB11_I

DPI Pin Buffer 11 Input

SRU2_PIN2

(0x01C12)

DPI Pin Buffer 13 Input

Reset = 0x00450000

Loading...

Loading...