Making Connections in the SRUs

4-62 ADSP-21368 SHARC Processor Hardware Reference

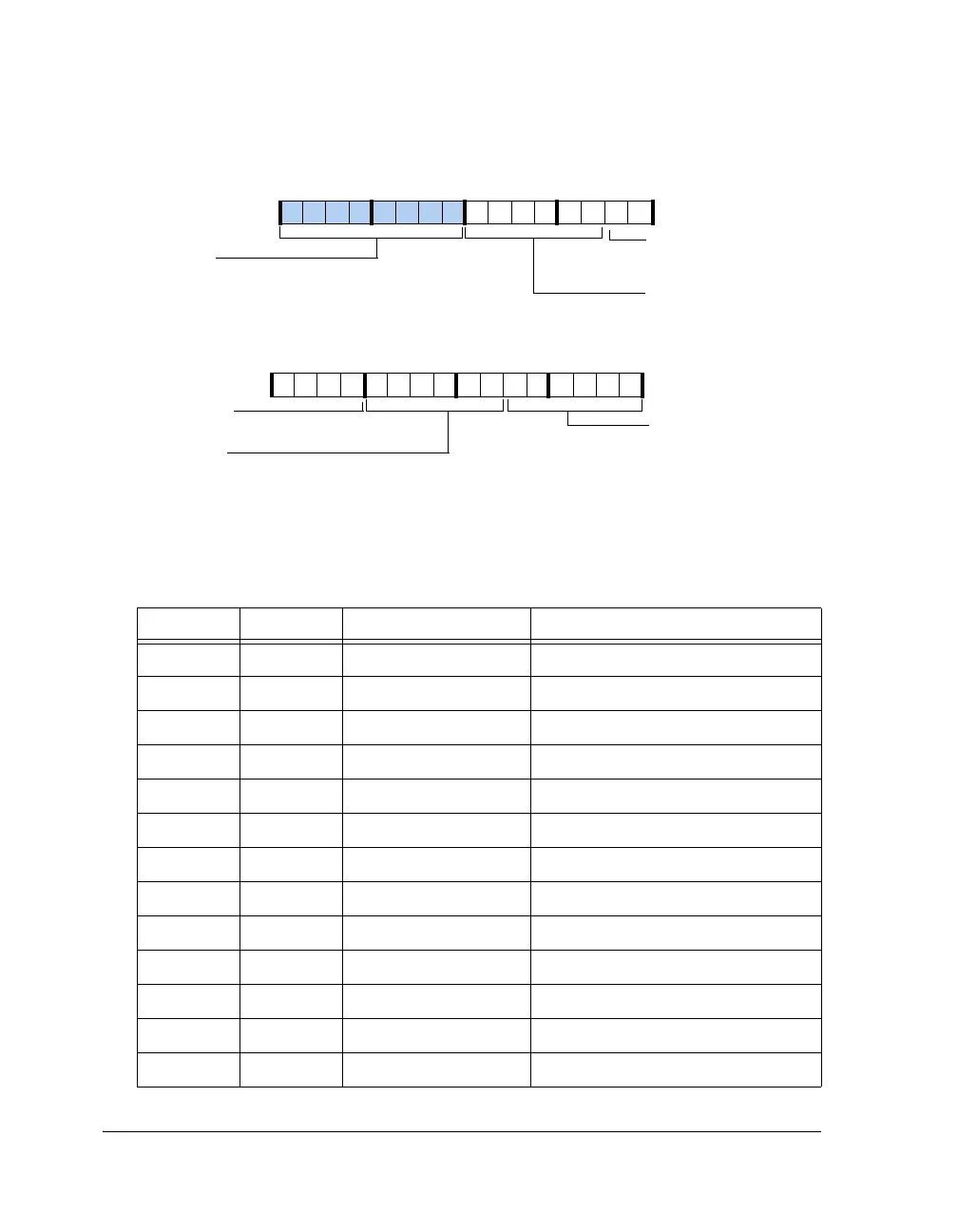

Figure 4-52. SRU2_PBEN2 Register

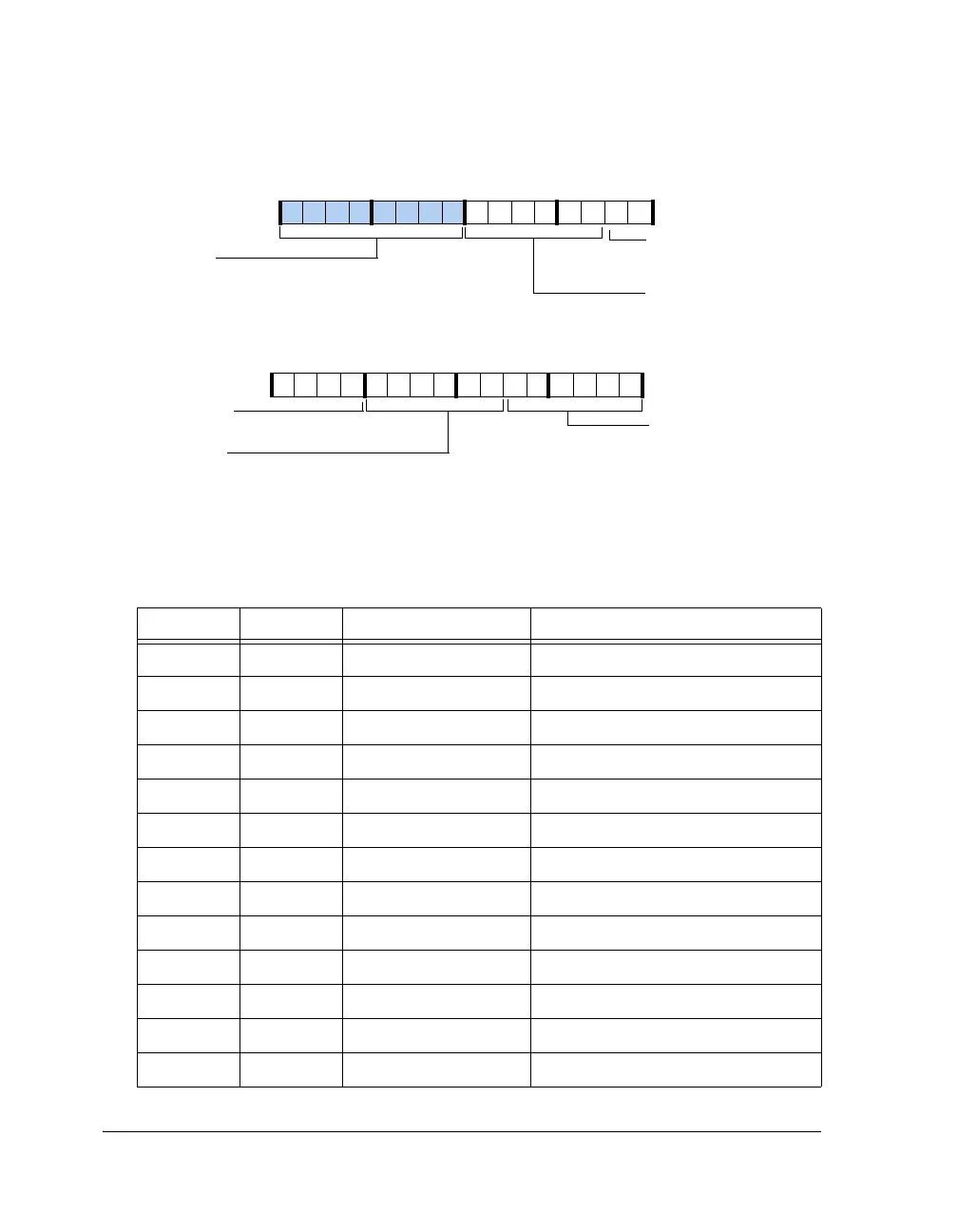

Table 4-13. Group C Signals

Binary Decimal Signal Description

000000 00 LOGIC_LEVEL_LOW Logic level low (0)

000001 01 LOGIC_LEVEL_HIGH Logic level high (1)

000010 02 EXT_MISC_0 Miscellaneous control 0

000011 03 EXT_MISC_1 Miscellaneous control 1

000100 04 EXT_MISC_2 Miscellaneous control 2

000101 05 TIMER0_PE_O Enable for timer 0 output

000110 06 TIMER1_PE_O Enable for timer 1 output

000111 07 TIMER2_PE_O Enable for timer 2 output

001000 08 UART0_TX_PE_0 Pin enable for UART 0 transmitter

001001 09 UART1_TX_PE_0 Pin enable for UART 1 transmitter

001010 10 SPIMISO_PE_O Pin enable for MISO from SPI

001011 11 SPIMOSI_PE_O Pin enable for MOSI froM SPI

001100 12 SPICLK_PE_O Pin enable for CLK from SPI

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000000000001100

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0010110010110010

DPI_PBEN13_I

DPI Pin Buffer Enable 13

Input

DPI_PBEN14_I

DPI Pin Buffer Enable 14

Input

DPI_PBEN13_I

DPI_PBEN12_I

DPI Pin Buffer Enable 12 Input

DPI_PBEN11_I

DPI Pin Buffer Enable 11

Input

SRU2_PBEN2

(0x01C22)

DPI Pin Buffer Enable 13 Input

Reset = 0x00185964

Loading...

Loading...