ADSP-21368 SHARC Processor Hardware Reference 5-77

Serial Ports

The DMA channels operate similarly to the processor’s data address gen-

erators (DAGs). Each channel has an index register (

IISPxy) and a modify

register (IMSPxy) for setting up a data buffer in internal memory. It is nec-

essary to initialize the index register with the starting address of the data

buffer. After it transfers each serial I/O word to (or from) the SPORT, the

DMA controller adds the modify value to the index register to generate

the address for the next DMA transfer. The modify value in the IM register

is a signed integer, which provides capability for both incrementing and

decrementing the buffer pointer.

Each DMA channel has a count register (CSPxA/CSPxB) which must be ini-

tialized with a word count that specifies the number of words to transfer.

The count register decrements after each DMA transfer on the channel.

When the word count reaches zero, the SPORT generates an interrupt,

then automatically disables the DMA channel.

Each SPORT DMA channel also has a chain pointer register (CPSPxy).

The CPSPxy register functions are used in chained DMA operations. For

more information on SPORT DMA chaining registers, see Table 5-12 on

page 5-76.

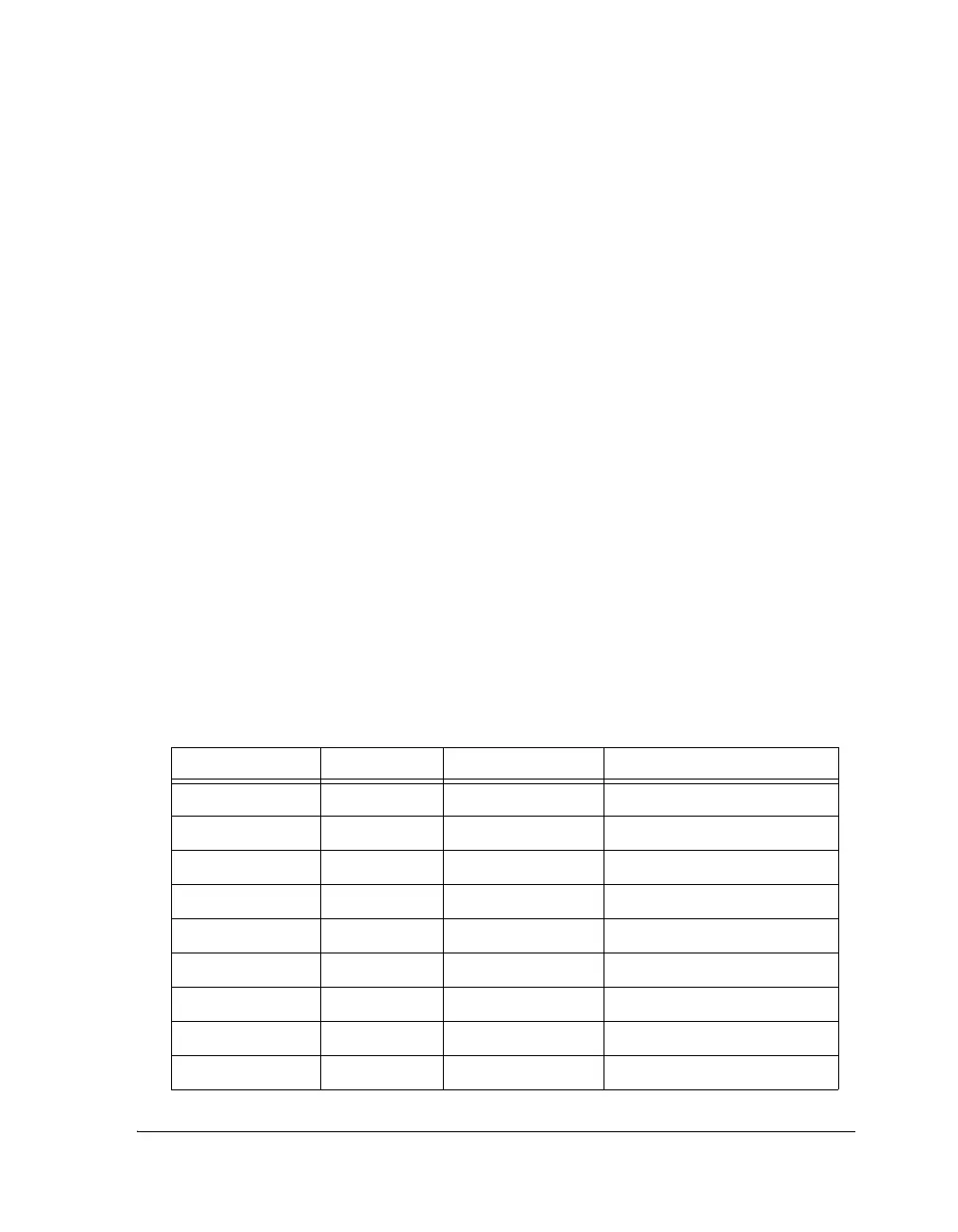

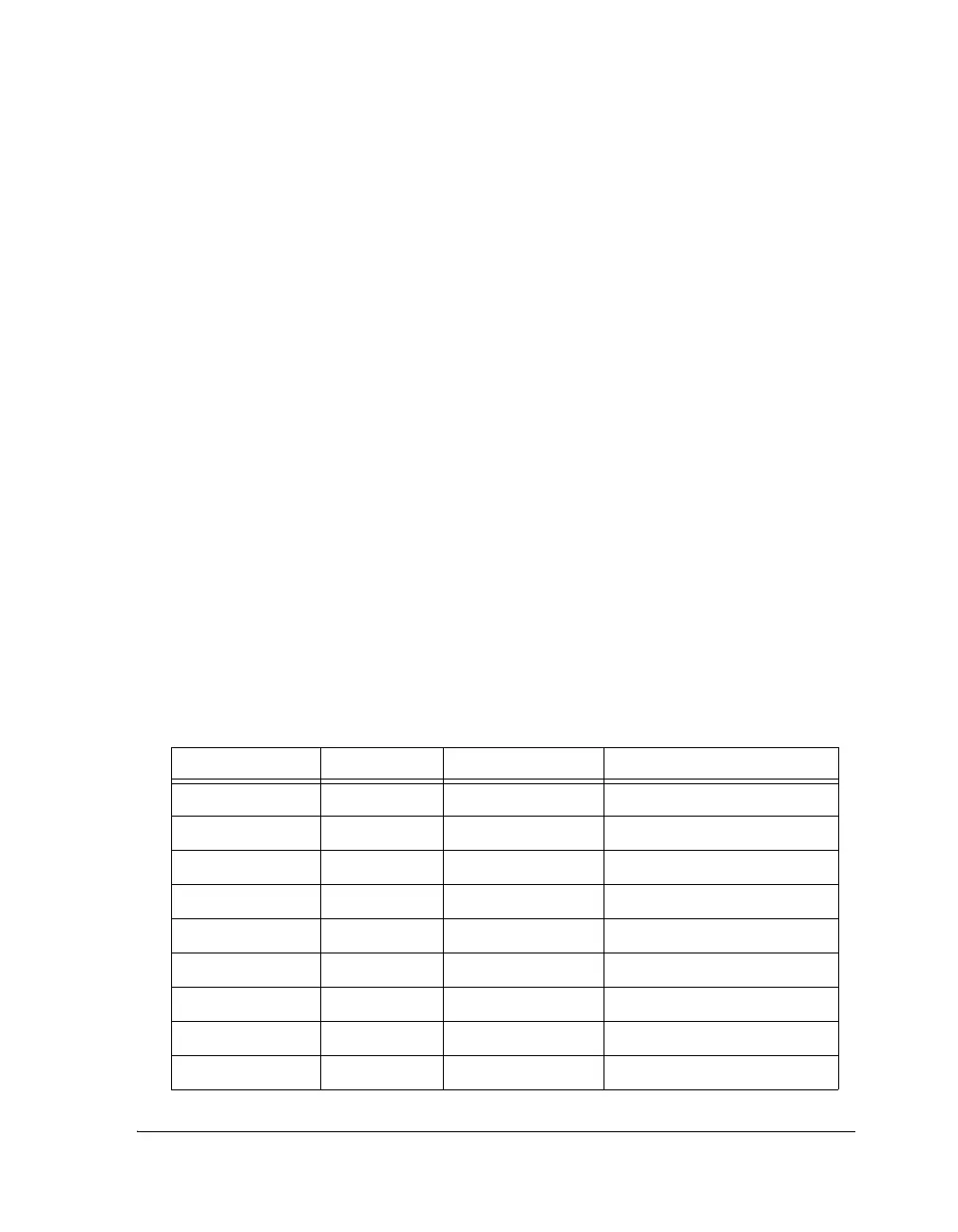

Table 5-13. SPORT DMA Parameter Registers Addresses

Register Address DMA Channel SPORT Buffer

IISP0A 0xC40 0 RXSP0A or TXSP0A

IMSP0A 0xC41 0 RXSP0A or TXSP0A

CSP0A 0xC42 0 RXSP0A or TXSP0A

CPSP0A 0xC43 0 RXSP0A or TXSP0A

IISP0B 0xC44 1 RXSP0B or TXSP0B

IMSP0B 0xC45 1 RXSP0B or TXSP0B

CSP0B 0xC46 1 RXSP0B or TXSP0B

CPSP0B 0xC47 1 RXSP0B or TXSP0B

IISP1A 0xC48 2 RXSP1A or TXSP1A

Loading...

Loading...