Moving Data Between SPORTs and Internal Memory

5-80 ADSP-21368 SHARC Processor Hardware Reference

When programming a SPORT channel (either A or B) as a transmitter,

only the corresponding

TXSPxA and TXSPxB SPORT buffer becomes active,

while the receive buffers (RXSPxA and RXSPxB) remain inactive. Similarly,

when the SPORT channel A and B is programmed as a receiver, only the

corresponding RXSP0A and RXSP0B SPORT buffer is activated.

When performing core-driven transfers, write to the buffer designated by

the SPTRAN bit setting in the SPCTLx registers. For DMA-driven transfers,

the SPORT logic performs the data transfer from internal memory

to/from the appropriate buffer depending on the

SPTRAN bit setting. If the

inactive SPORT data buffers are read or written to by the core while the

port is enabled, the core hangs. For example, if a SPORT is programmed

to be a transmitter, while at the same time the core reads from the receive

buffer of the same SPORT, the core hangs just as it would if it were read-

ing an empty buffer that is currently active. This locks up the core until

the SPORT is reset.

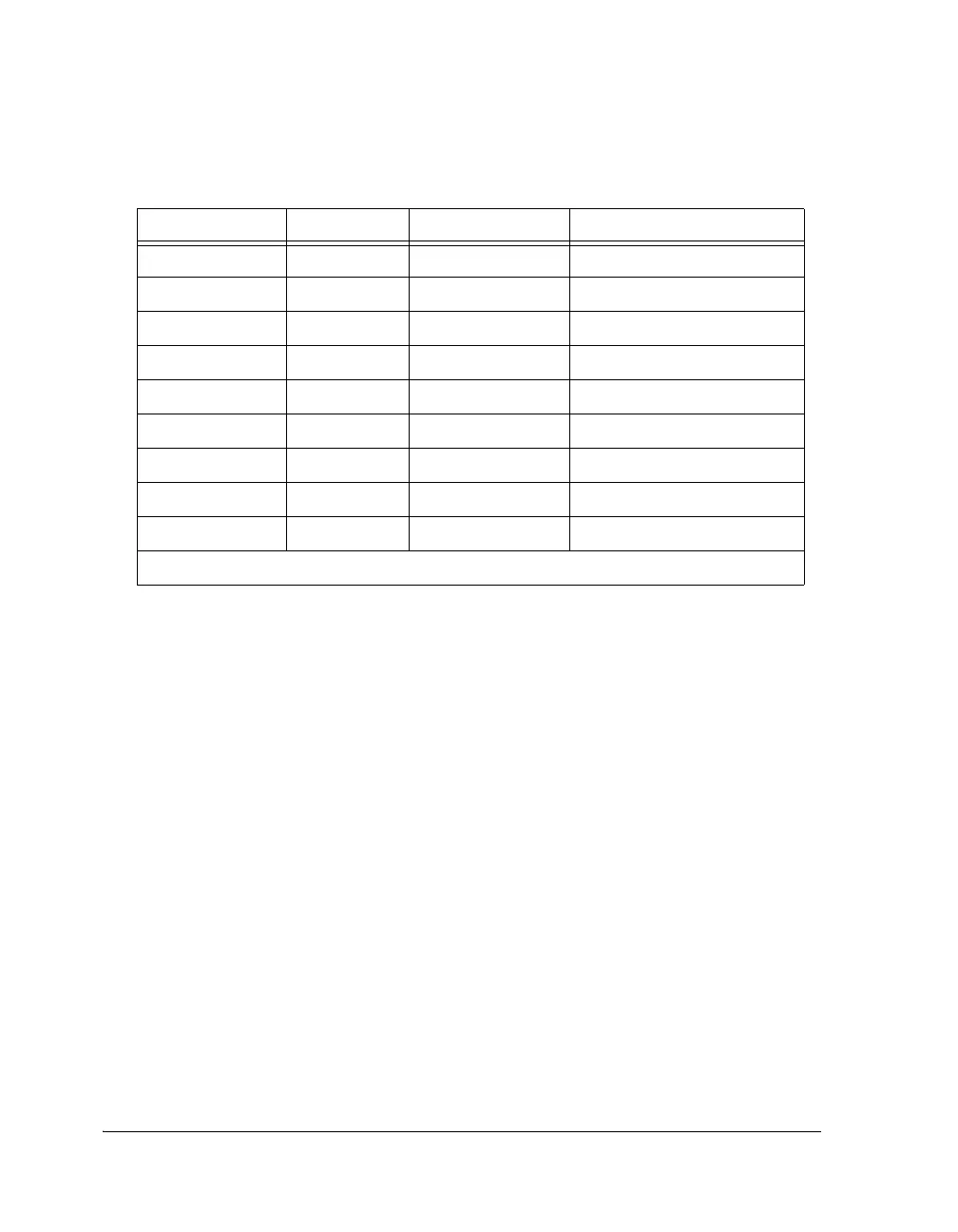

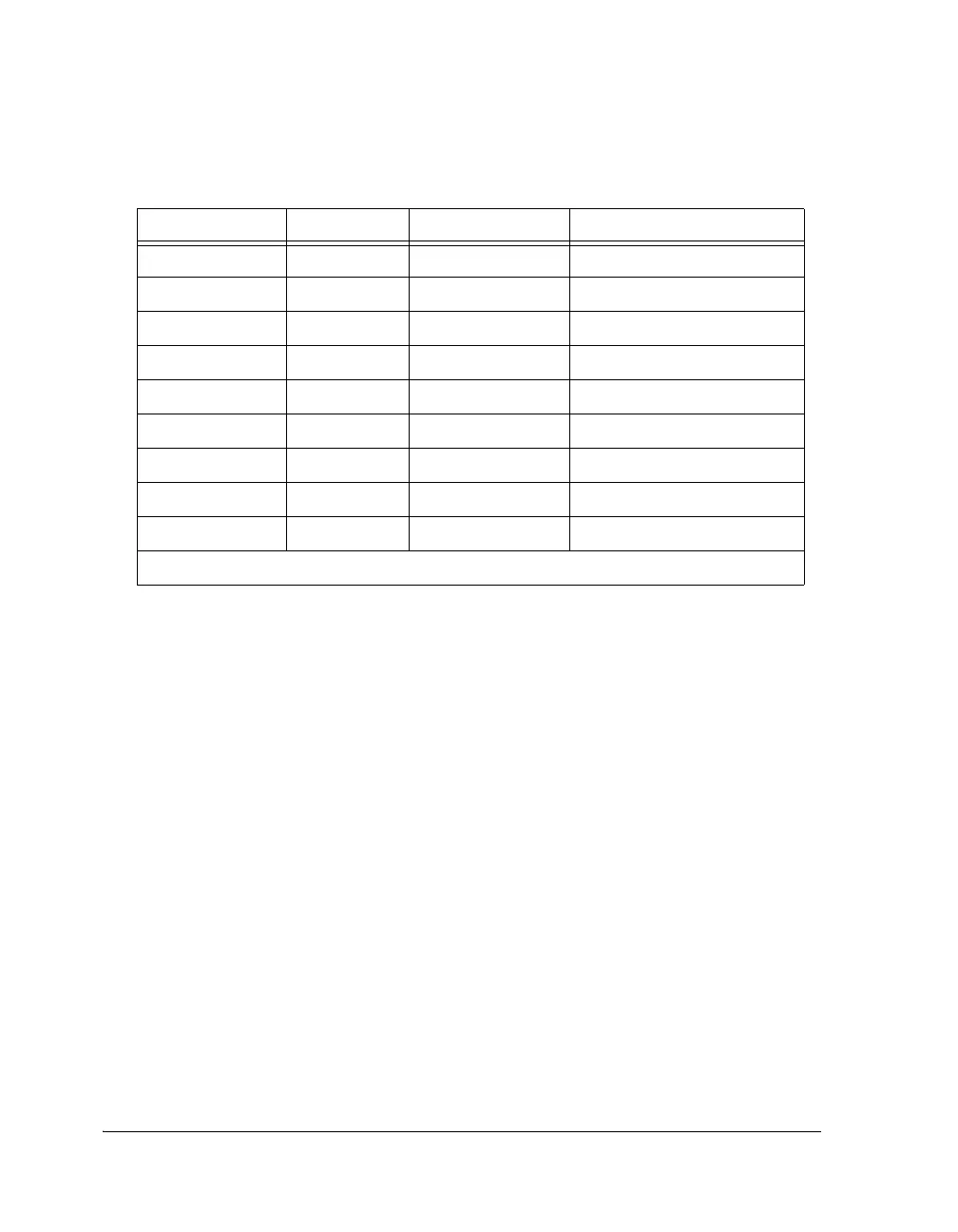

CPSP6B 0x4847 13 RXSP6B or TXSP6B

IISP7A 0x4848 14 RXSP7A or TXSP7A

IMSP7A 0x4849 14 RXSP7A or TXSP7A

CSP7A 0x484A 14 RXSP7A or TXSP7A

CPSP7A 0x484B 14 RXSP7A or TXSP7A

IISP7B 0x484C 15 RXSP7B or TXSP7B

IMSP7B 0x484D 15 RXSP7B or TXSP7B

CSP7B 0x484E 15 RXSP7B or TXSP7B

CPSP7B 0x484F 15 RXSP7B or TXSP7B

Reserved (0x850 to 0x85F)

Table 5-13. SPORT DMA Parameter Registers Addresses (Cont’d)

Register Address DMA Channel SPORT Buffer

Loading...

Loading...