13-2 ADSP-21368 SHARC Processor Hardware Reference

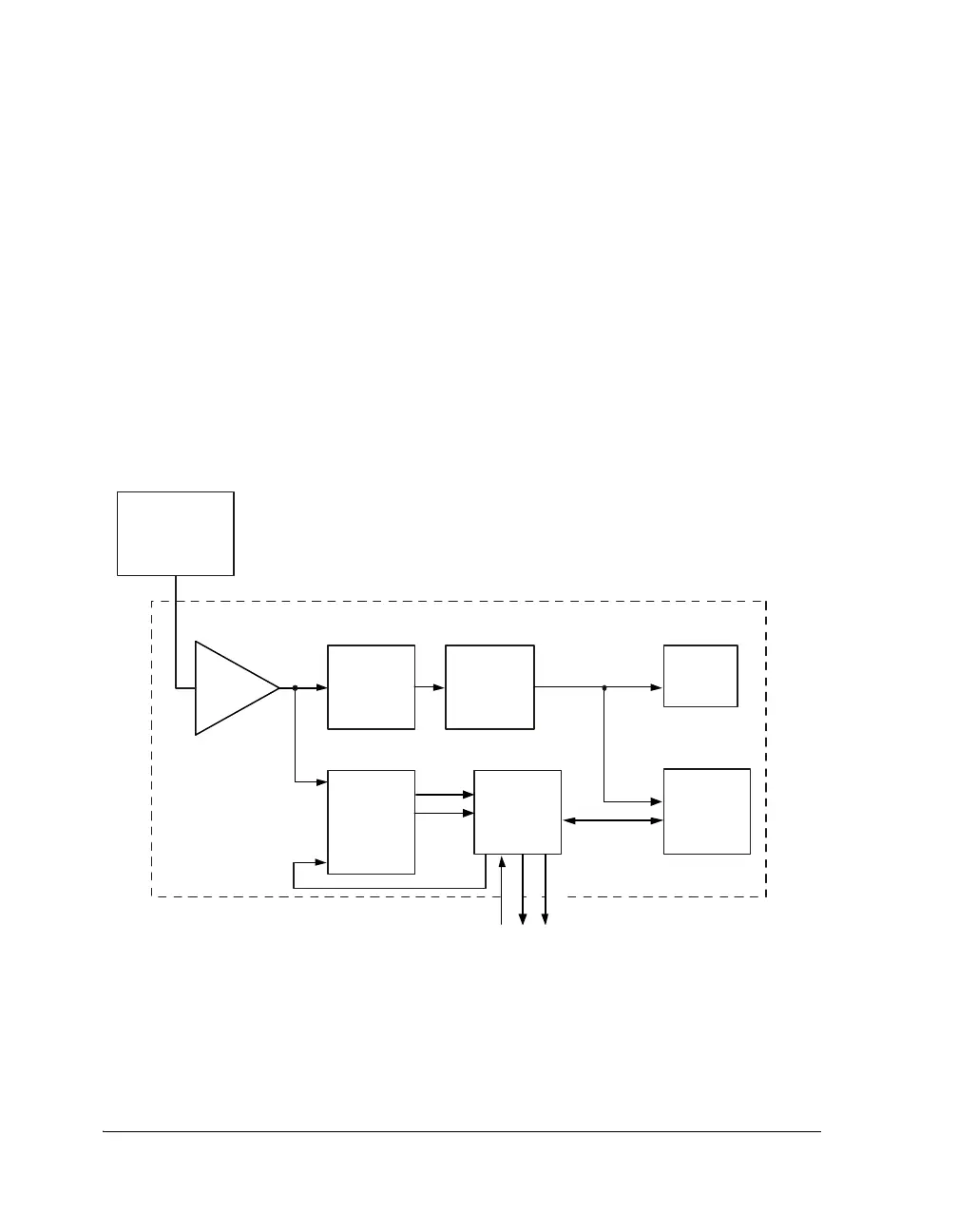

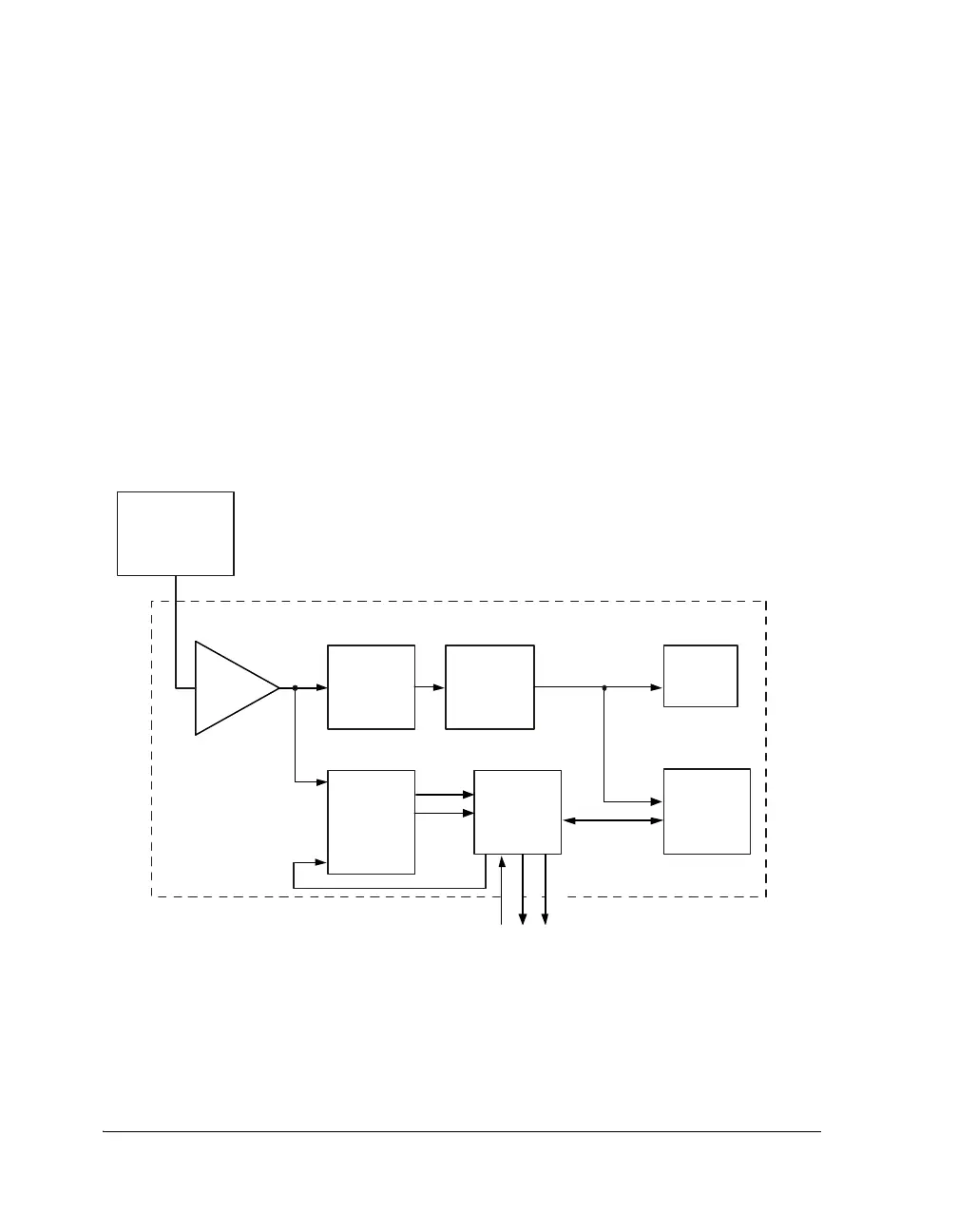

The core phase-locked loop (PLL) has been designed to provide clocking

for the processor core. Although the performance specifications of this

PLL are appropriate for the core, they have not been optimized or speci-

fied for precision data converters where jitter directly translates into time

quantization errors and distortion.

As shown in Figure 13-1, the PCGs can accept clock inputs either directly

from the external oscillator (or discrete crystal) connected to the

CLKIN

pin, from the peripheral clock (PCLK), or from any of the 20 DAI pins.

This allows a design to contain an external clock with performance specifi-

cations appropriate for the application target.

Note that clock and frame sync signals generated by the serial ports are

also subject to these jitter problems because the SPORT clock is generated

from the core clock. However, a SPORT can produce data output while

Figure 13-1. Clock Inputs

EXTERNAL

OSCI LLATOR

CO RE

PLL

SHARC ADSP-213xx

PRECISION

CLOCK

GE NE R ATO RS

(A- D)

M/N

CORE CLOCK

GENERATOR

SERIAL

PORT

SIGNAL

ROUTING

UNIT

CORE

CORE CLOCK

BUFFER

AM P

SCLK

FSYNC

INPUT0

INPUT1

FSYNC

PCLK

SCLK

Loading...

Loading...