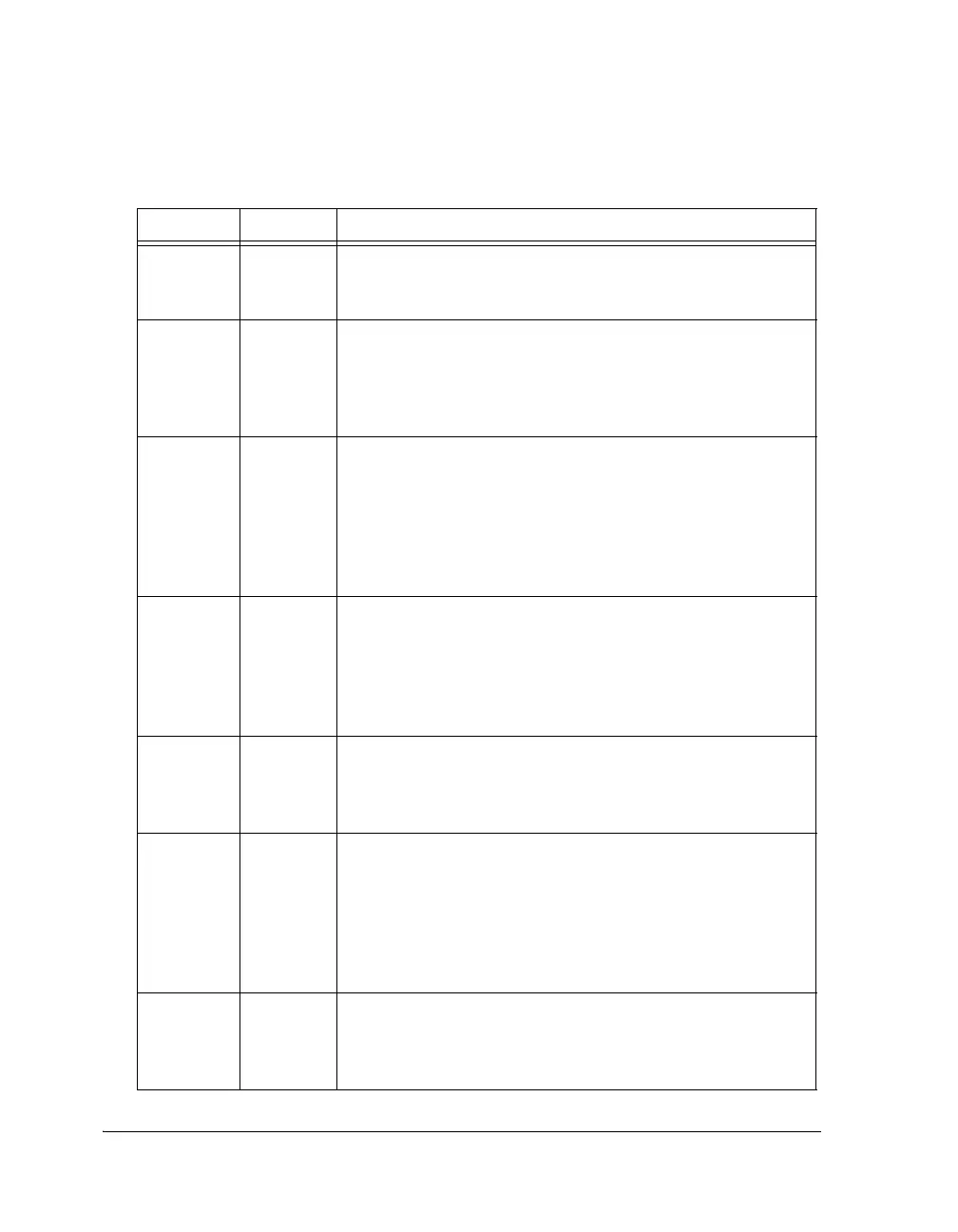

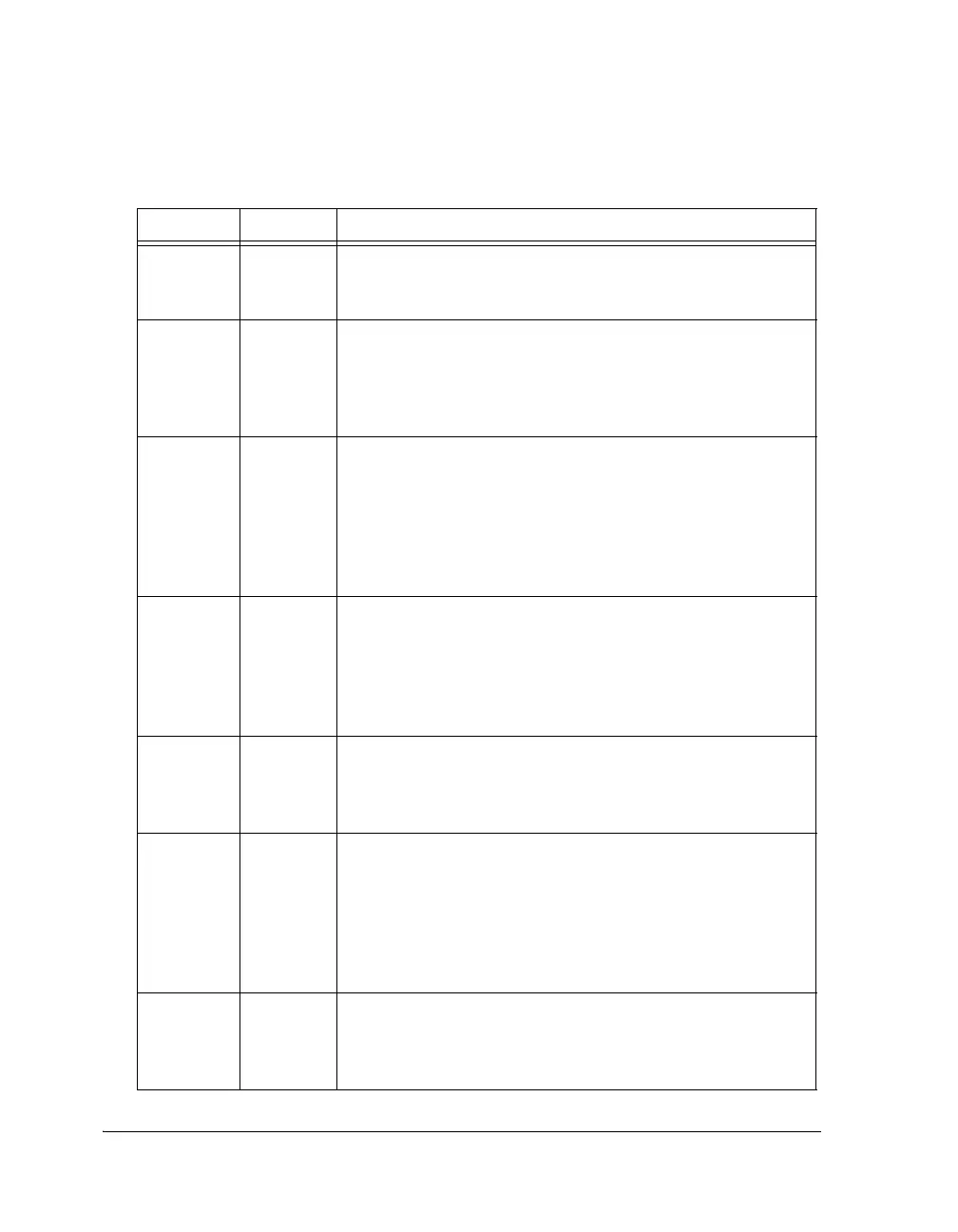

External Port Registers

A-18 ADSP-21368 SHARC Processor Hardware Reference

Table A-5. AMICTLx Register Bit Descriptions

Bit Name Description

0AMIENAMI Enable.

0 = AMI is disabled

1 = AMI is enabled

2–1 BW External Data Bus Width.

00 = 8 bits

01 = 16 bits

10 = 32 bits

11 = Reserved

3PKDISDisable Packing/Unpacking.

0 = 8/16-bit data received packed to 32-bit data. Similarly, 32-bit

data to be transmitted is unpacked to two 16-bit data or four 8-bit

data.

1 = 8/16-bit data received zero-filled, for transmitted data only

16-bit or the 8-bit LSB part of the 32-bit data is written to external

memory.

4MSWFMost Significant Word First. Applicable only with packing dis-

abled (PKDIS=0).

0 = 1st 8/16-bit word read/write occupies the least significant posi-

tion in the 32-bit packed word.

1 = 1st 8/16-bit word read/write occupies the most significant posi-

tion in the 32-bit packed word.

5ACKENEnable the ACK pin.

If enabled, reads/writes to devices have to be extended by the corre-

sponding devices by pulling ACK low. When ACKEN is set then

the ACK pin is sampled after the waitstate value is programmed.

10–6 WS Wait States.

00000 = Reserved (wait state value of 32 if used)

00001 = Reserved for internal use (can be used when the clock fre-

quencies are low)

00010 = wait state = 2 external port clock cycles

...

11111 = Wait state = 31 external port clock cycles

13–11 HC Bus Hold Cycle at the End of Write Access.

000 = Disable bus hold cycle

001 = Hold address for one external port clock cycle

010 = Hold address for two external port clock cycles

Loading...

Loading...