ADSP-21368 SHARC Processor Hardware Reference A-19

Register Reference

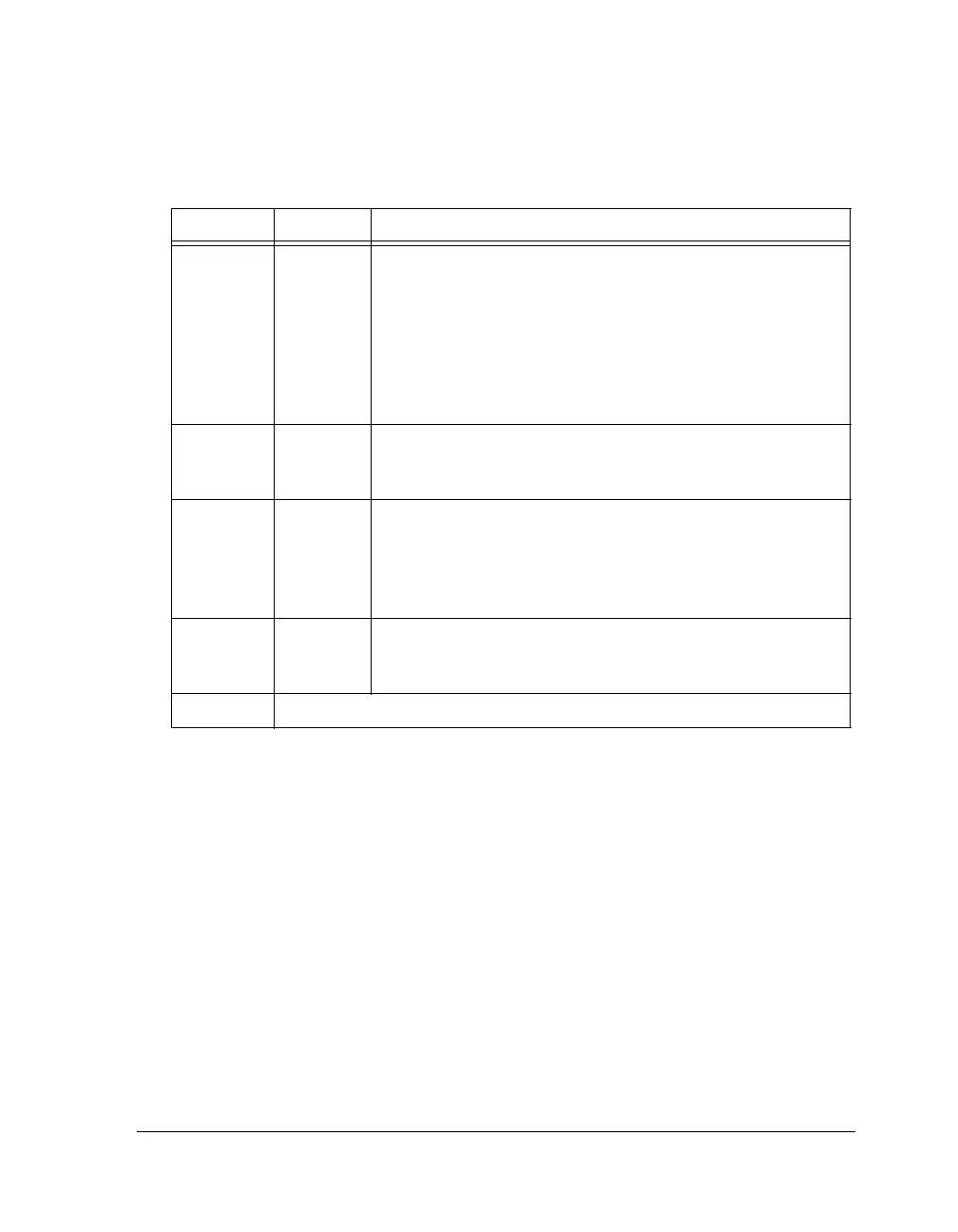

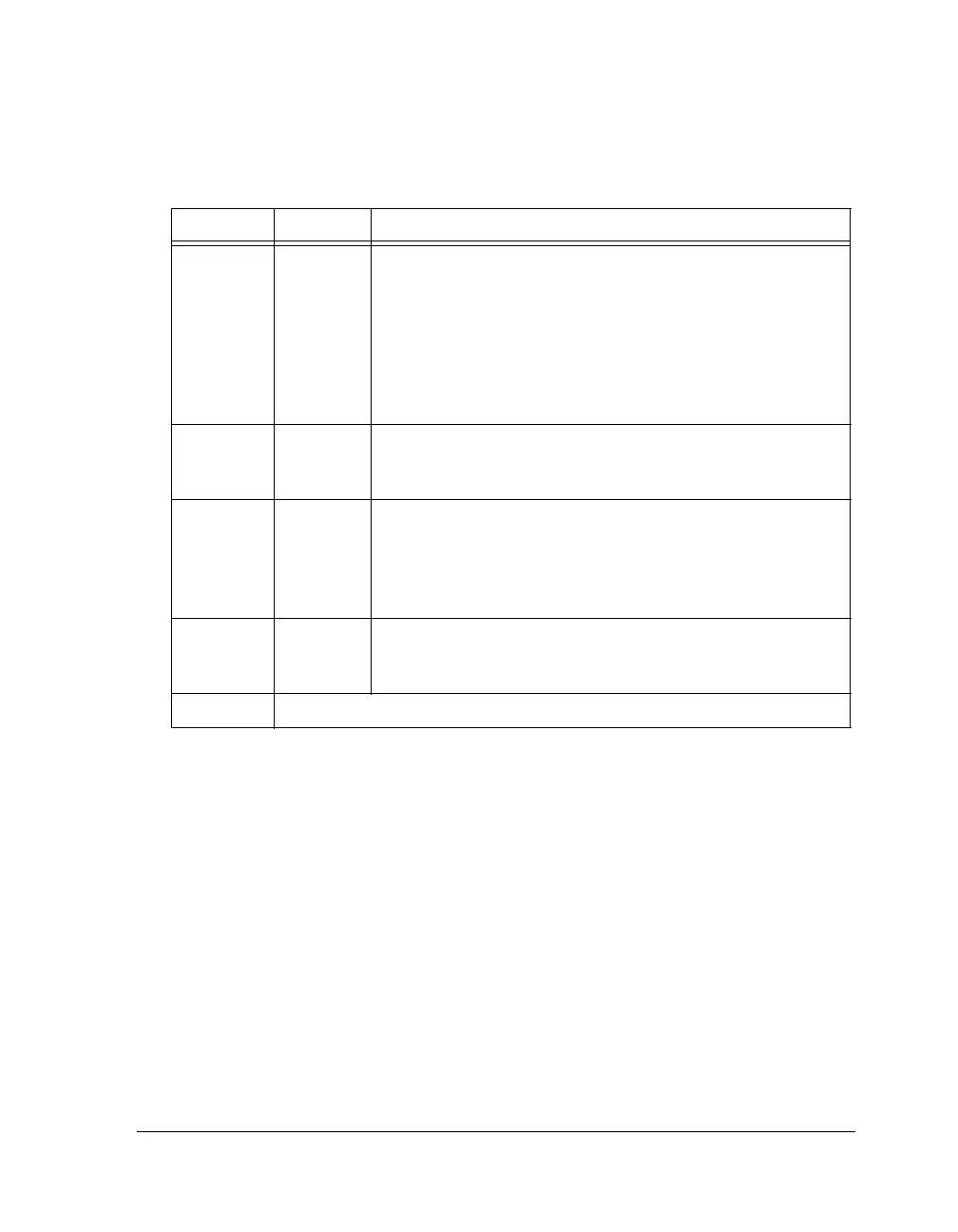

16–14 IC Bus Idle Cycle. Idle cycle to be inserted whenever read from exter-

nal memory is followed by a write to external memory – to avoid

contention. 'IC' EP clock cycles are ensured between a read to

write.

000 = 0 cycles, 001 = 1 cycle

010 = 2 cycles, 011 = 3 cycles

100 = 4 cycles, 101 = 5 cycles

110 = 6 cycles, 111 = 7 cycles

17 FLSH AMI Buffer Flush (Write-only).

0 = Buffer holds the data

1 = Flush the buffer

20–18 RHC Read Hold Cycle at the End of Read Access. Controls the delay

between two reads.

000 = Disable read hold cycle

001 = Hold address for one external port clock cycle

010 = Hold address for two external port clock cycles

21 NO_OPT Disable Predictive Reads.

Default is predictive reads are enabled. For more information, see

“SDRAM Read Optimization” on page 3-75.

31–22 Reserved

Table A-5. AMICTLx Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...