ADSP-21368 SHARC Processor Hardware Reference A-39

Register Reference

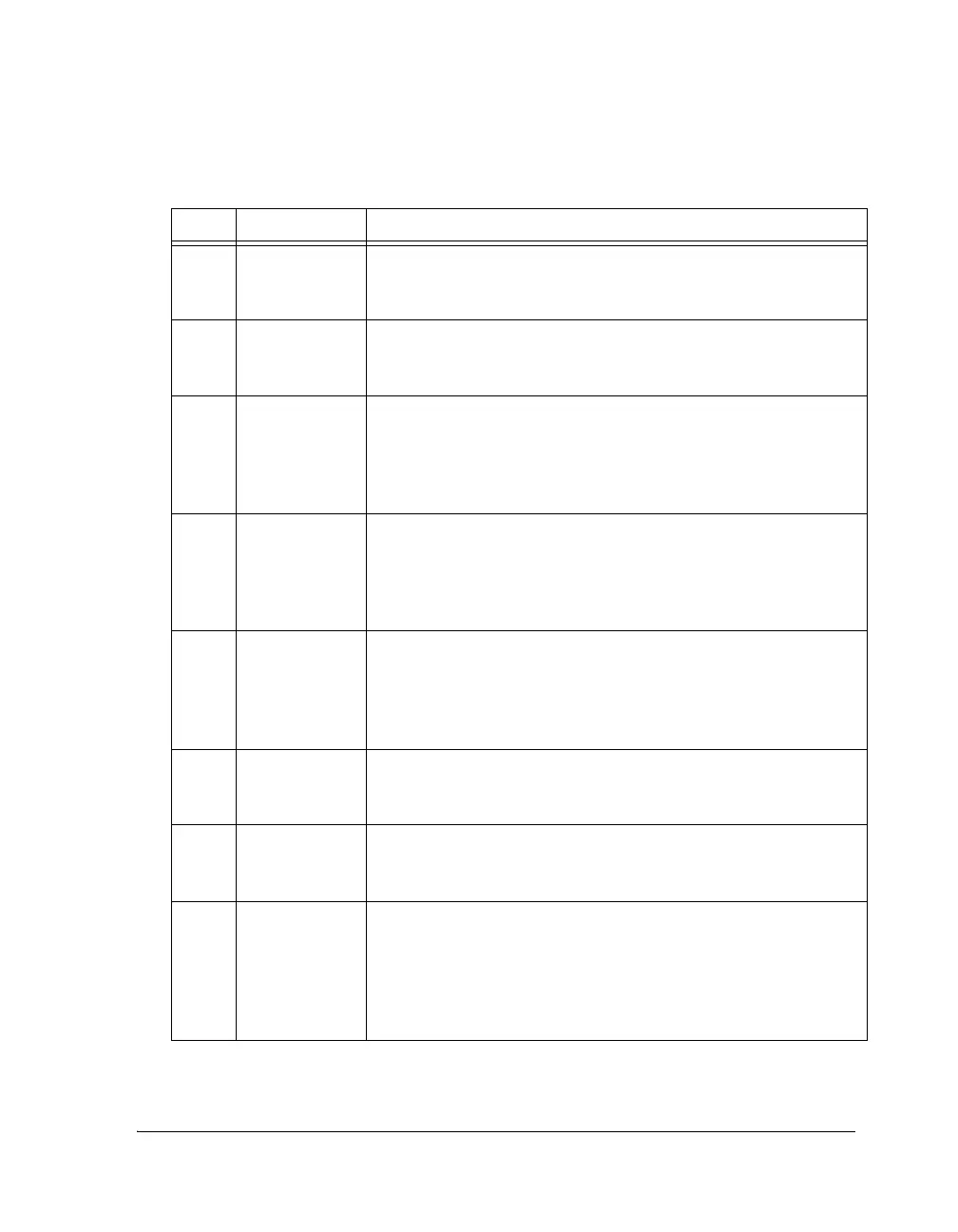

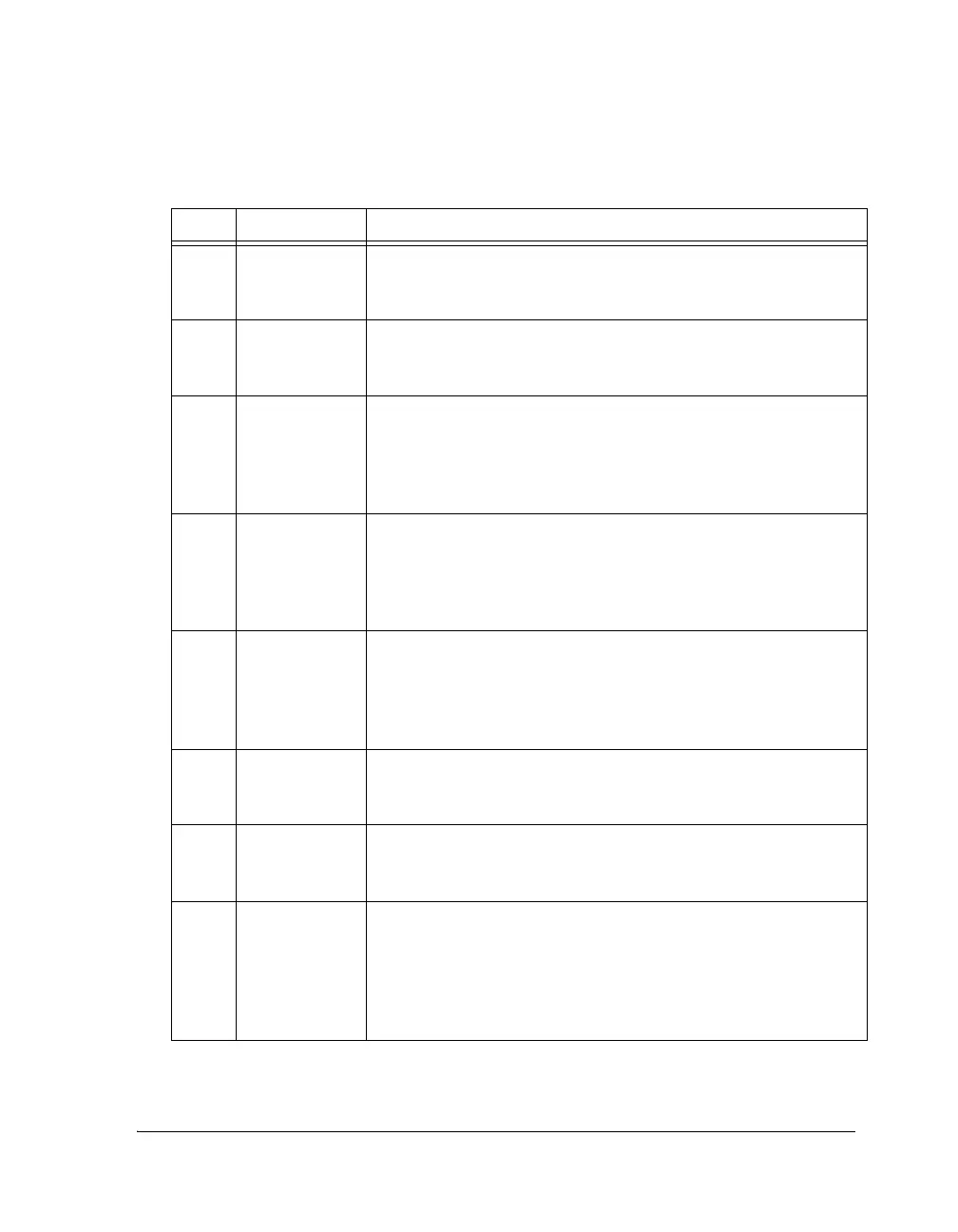

20 SDEN_B Enable Channel B Serial Port DMA.

0 = Disable serial port channel B DMA

1 = Enable serial port channel B DMA

21 SCHEN_B Enable Channel B Serial Port DMA Chaining.

0 = Disable serial port channel B DMA chaining

1 = Enable serial port channel B DMA chaining

22 FS_BOTH FS Both Enable.

0 = Issue WS if data is present in either transmit buffer

1 = Issue WS if data is present in both transmit buffers

This bit is reserved when the SPORT is in packed I

2

S, multichannel,

I

2

S and left-justified sample pair modes.

23 BHD Buffer Hang Disable.

0 = Indicates a core stall. The core stalls when it tries to write to a full

transmit buffer or read an empty receive buffer FIFO.

1 = Ignore a core hang

This bit applies to all modes.

24 SPEN_B Enable Channel B Serial Port.

0 = Serial port A channel disabled

1 = Serial port A channel enabled

This bit is reserved when the SPORT is in packed I

2

S and multichan-

nel modes.

25 SPTRAN Data Direction Control.

0 = Enable receive buffers

1 = Activate transmit buffers

26 DERR_B

(TUVF_B or

ROVF_B)

Channel B Error Status (sticky, read-only). Indicates if the serial

transmit operation has underflowed or a receive operation has over-

flowed in the channel B data buffer.

28–27 DXS_B Channel B Data Buffer Status (read-only). Indicates the status of the

serial port’s channel B data buffer as follows:

11 = Full

00 = Empty

10 = Partially full

This bit is reserved when the SPORT is in multichannel mode.

Table A-8. SPCTLx Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...