ADSP-21368 SHARC Processor Hardware Reference A-77

Register Reference

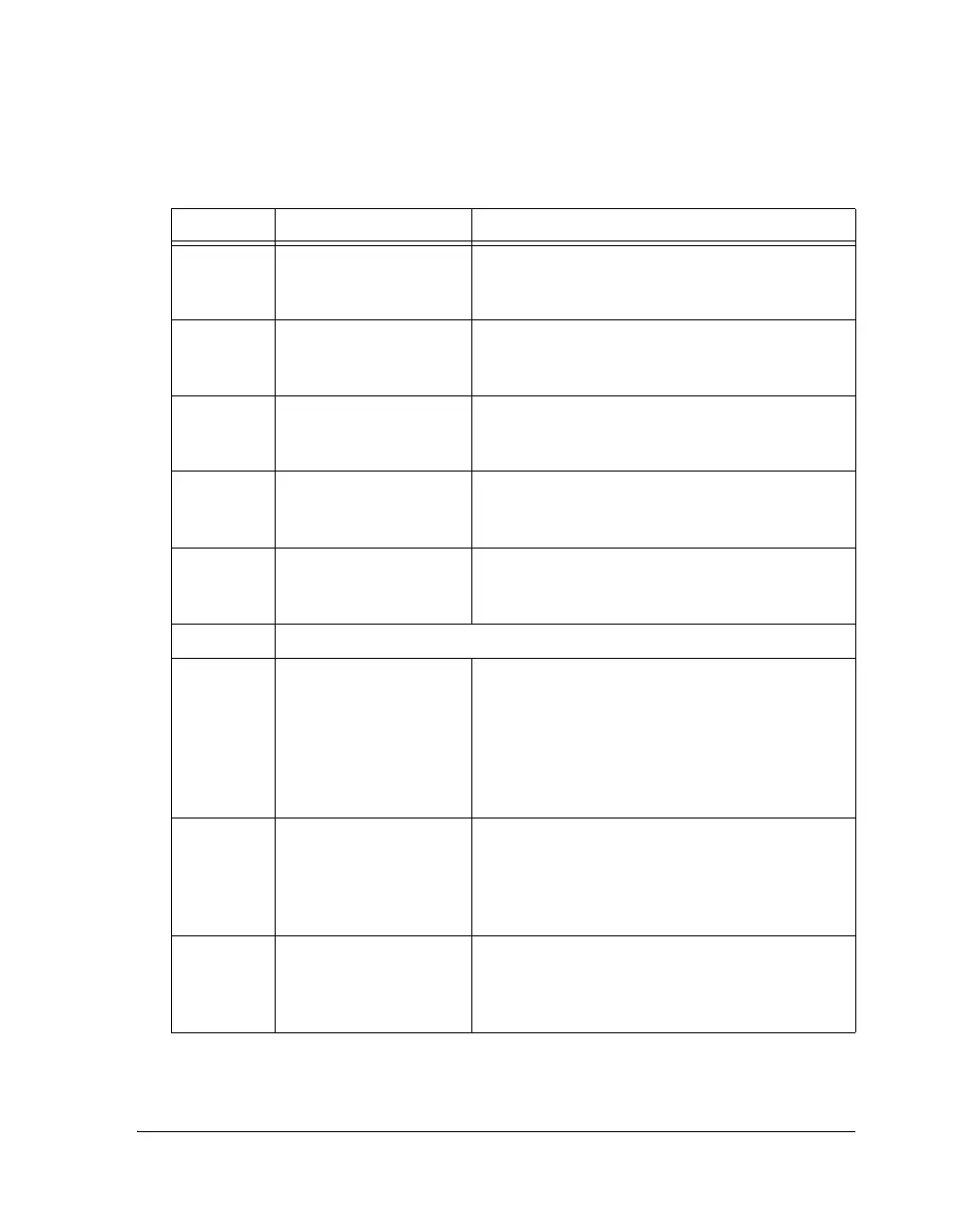

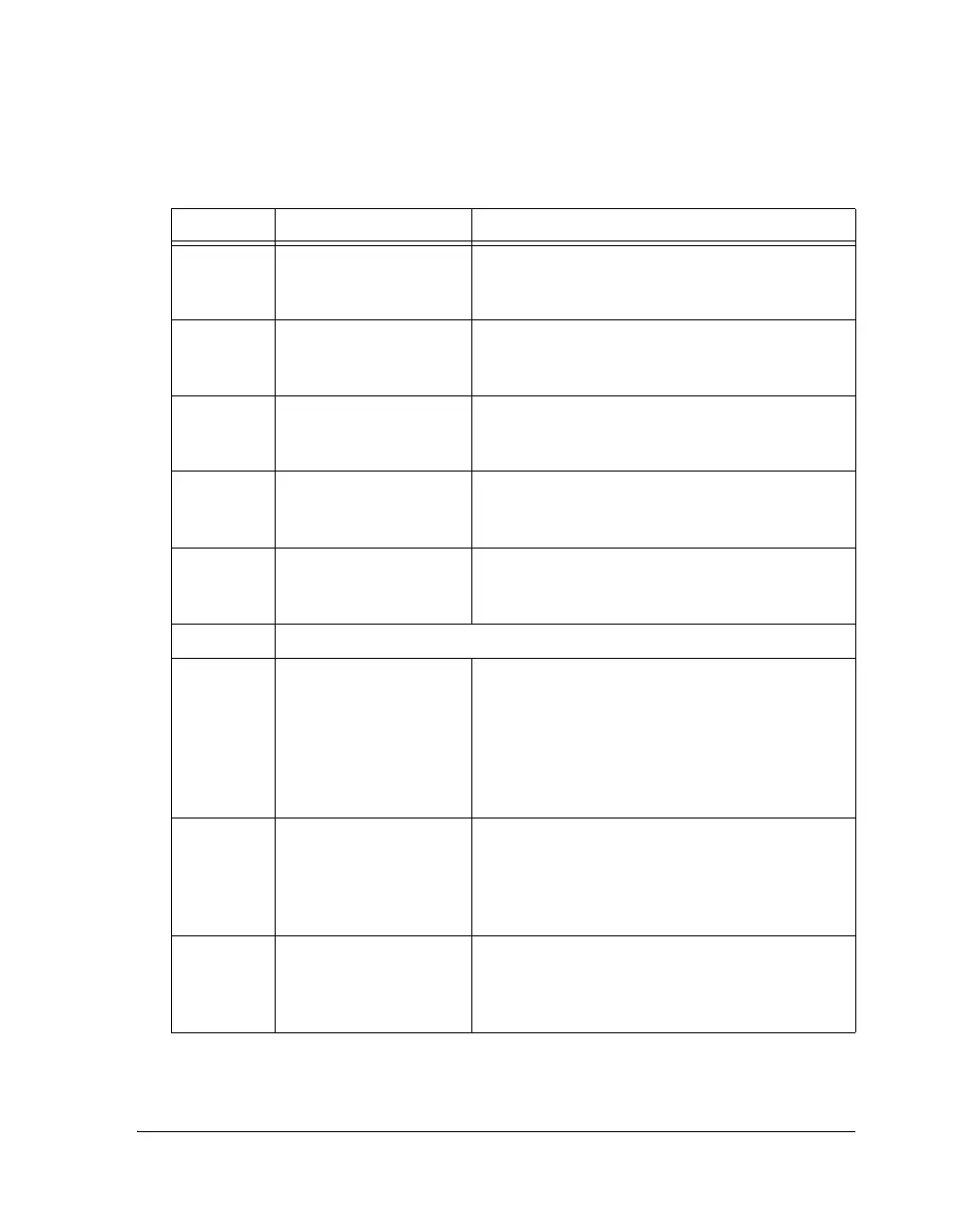

15 IDP_P16_PDAPMASK Parallel Data Acquisition Port Mask.

0 = Input data from DAI_16/ADDR3 is masked

1 = Input data from DAI_16/ADDR3 is unmasked

16 IDP_P17_PDAPMASK Parallel Data Acquisition Port Mask.

0 = Input data from DAI_17/ADDR4 is masked

1 = Input data from DAI_17/ADDR4 is unmasked

17 IDP_P18_PDAPMASK Parallel Data Acquisition Port Mask.

0 = Input data from DAI_18/ADDR5 is masked

1 = Input data from DAI_18/ADDR5 is unmasked

18 IDP_P19_PDAPMASK Parallel Data Acquisition Port Mask.

0 = Input data from DAI_19/ADDR6 is masked

1 = Input data from DAI_19/ADDR6 is unmasked

19 IDP_P20_PDAPMASK Parallel Data Acquisition Port Mask.

0 = Input data from DAI_20/ADDR7 is masked

1 = Input data from DAI_20/ADDR7 is unmasked

25–20 Reserved

26 IDP_PORT_SELECT Port Select: Input Pins Select.

0 = Data bits are read from DAI_P20–1

1 = Data bits are read from DATA31–12 and the

control signals come from DATA11-8 and the PDAP

can be operated through data pins alone (data and

controls can be completely routed through DATA

pins)

28–27 IDP_PDAP_PACKING Packing. Selects PDAP packing mode.

00 = 8- to 32-bit packing

01 = (11, 11, 10) to 32-bit packing

10 = 16- to 32-bit packing

11 = 20- to 32-bit packing. 12 LSBs are set to 0

29 IDP_PDAP_CLKEDGE PDAP (Rising or Falling) Clock Edge.

0 = Data is latched on the rising edge of the clock

(IDP0_CLK_I)

1 = Data is latched on the falling edge

Table A-24. IDP_PP_CTL Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...