Sample Rate Converter Registers

A-98 ADSP-21368 SHARC Processor Hardware Reference

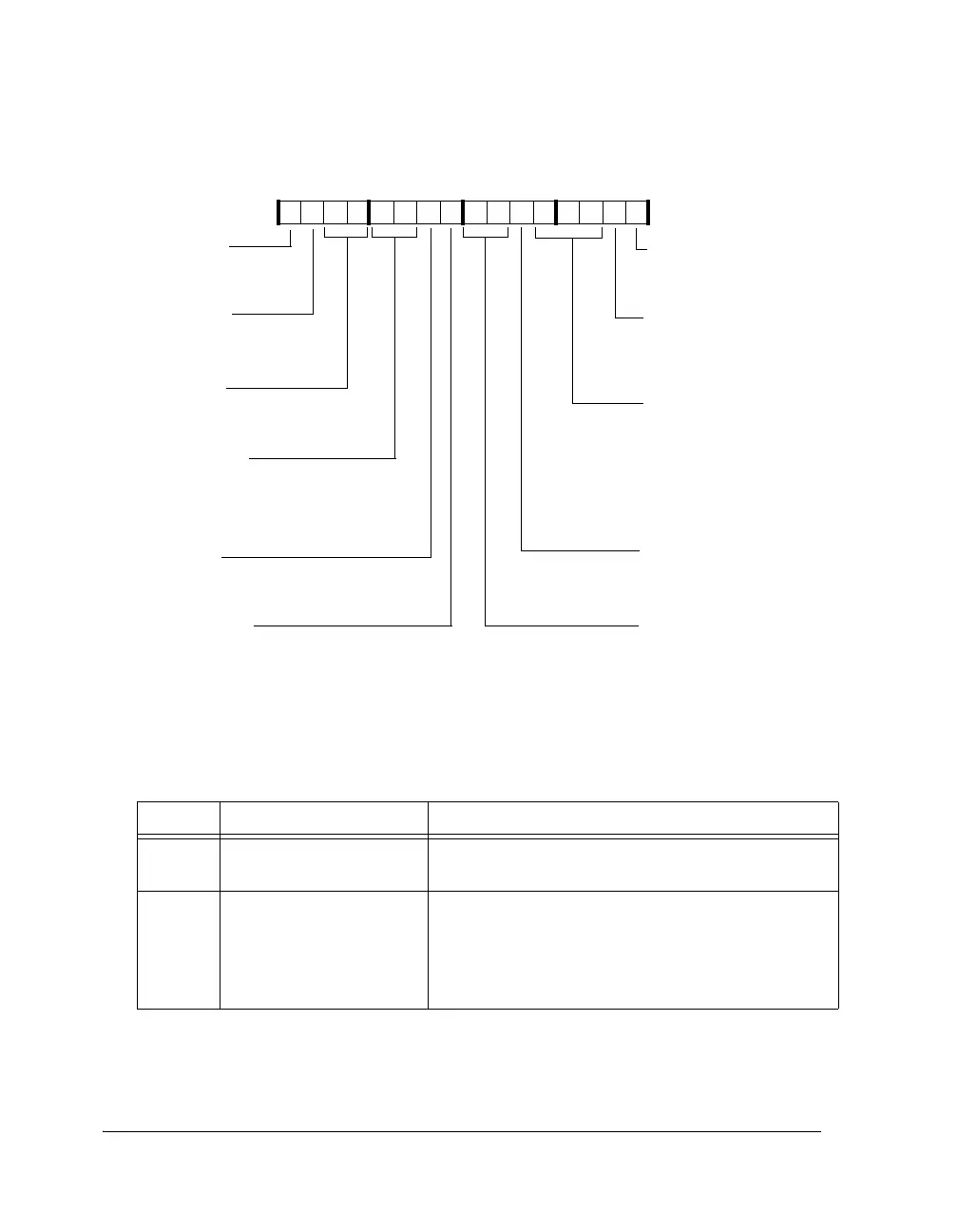

Figure A-37. SRCCTL0 Register (Bits 0–15)

Table A-42. SRCCTL0 Register Bit Descriptions

Bit Name Description

0 SRC0_HARD_MUTE Hard Mute. Hard mutes SRC 0.

1 = Mute (default)

1 SRC0_AUTO_MUTE Auto Hard Mute. Auto hard mutes SRC 0 when one of

the non-audio bits is asserted by the SPDIF receiver. See

Table A-39 on page A-95.

0 = No mute

1 = Mute (default)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

SRC0_HARD_MUTE

SRC0_RESET

SRC0 Reset

1=SRC enabled

0=SRC disabled

SRC0 Hard Mute Enable

1=Enabled

0=Disabled

SRC0_AUTO_MUTE

SRC0 Auto Hard Mute

Enable (from SPDIF RX)

1=Enabled

0=Disabled

SRC0_BYPASS

SRC0 De-emphasis Filter

1=Enabled

0=Disabled (default)

SRC0 Bypass Mode

1=Bypass enabled

0=Bypass disabled

SRC0_DEEMPHASIS

SRC0_MPHASE

SRC0 Matched-Phase Mode

1=Enabled

0=Disabled

SRC0_LENOUT

SRC0 Output Word Length

00=24-bit, 01=20-bit

10=18-bit, 11=16-bit

SRC0_SMODEOUT

SRC0 Serial Output Format

00=Left-justified (default)

01=I

2

S

10=TDM

11=Right-justified

SRC0_DITHER

SRC Dither Enable

1=Enable

0=Disable

SRC0 Soft Mute Enable

1=Mute (default)

0=No Mute

SRC0_SOFTMUTE

SRC0_SMODEIN

SRC0 Serial Input Format

000=Left-justified (Default)

001=I

2

S

010=TDM

100=24-bit right-justified

101=20-bit right-justified

110=18-bit right-justified

111=16-bit right-justified

SRCCTL0 (0x2490)

Loading...

Loading...