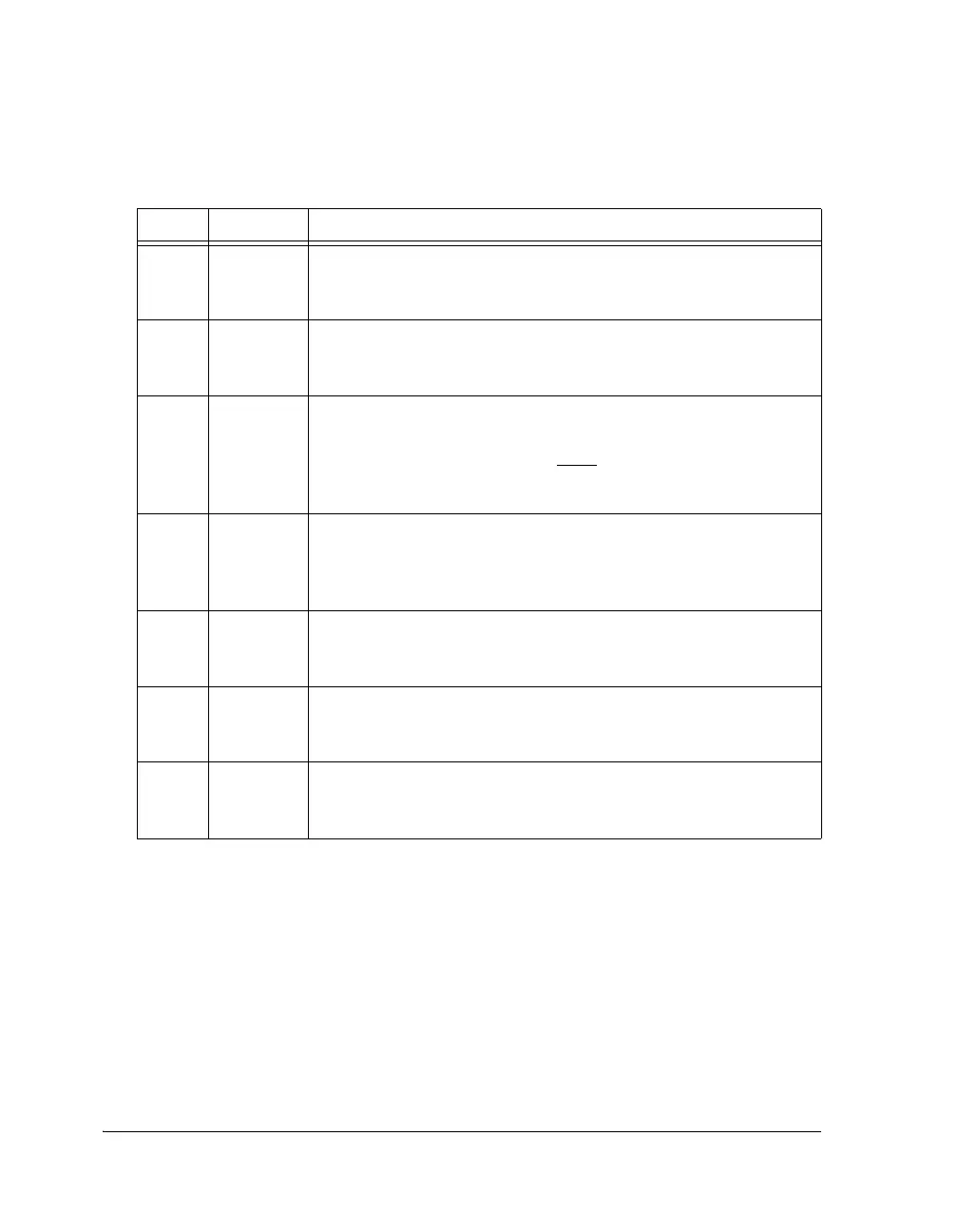

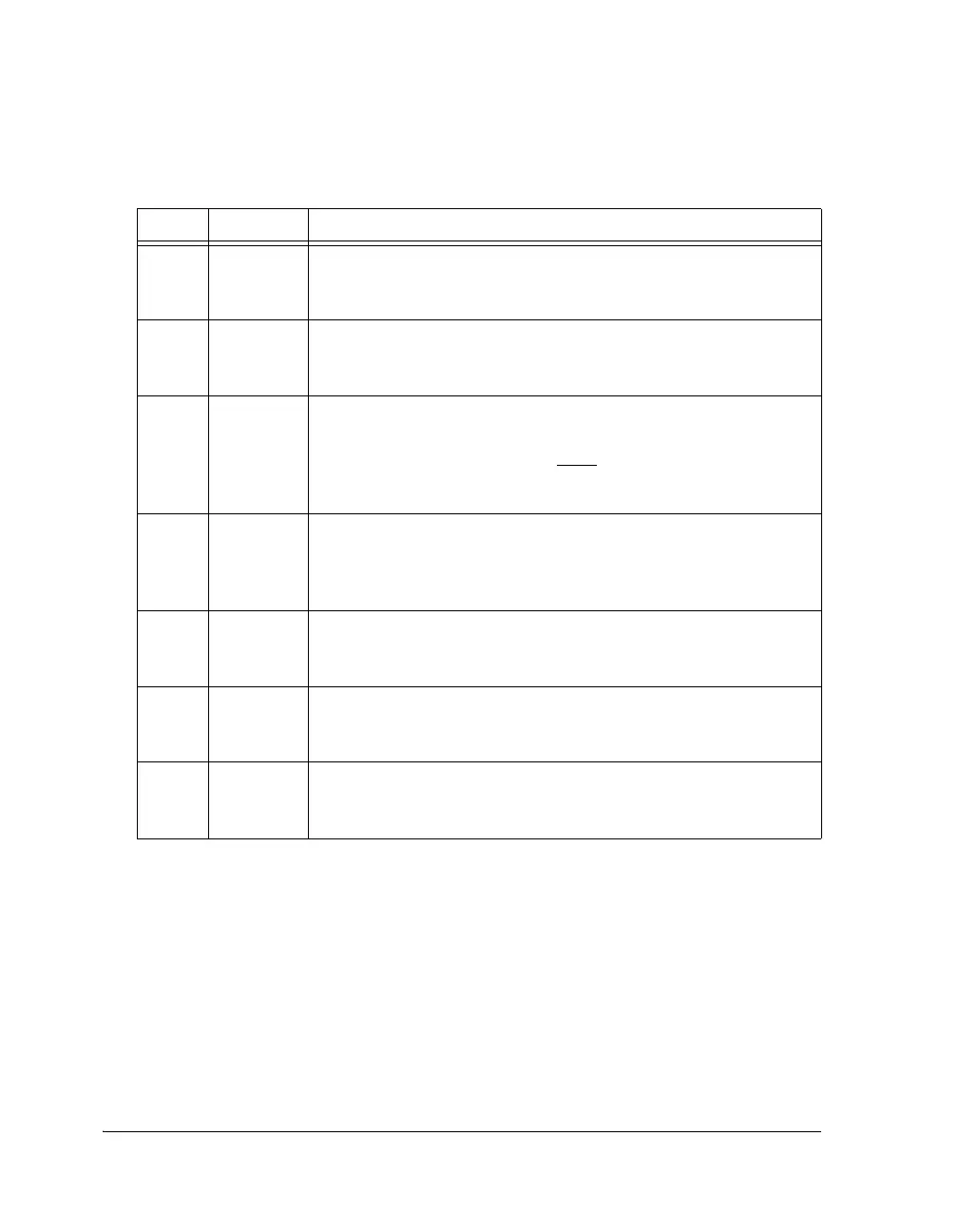

Interrupt Registers

B-26 ADSP-21368 SHARC Processor Hardware Reference

25 FLTUI Floating-Point Underflow Interrupt. When the processor is servicing

another interrupt, this bit indicates if the FLTUI interrupt is unmasked

(if set, = 1), or masked (if cleared, = 0).

26 FLTII Floating-Point Invalid Operation Interrupt. When the processor is ser-

vicing another interrupt, this bit indicates if the FLTII interrupt is

unmasked (if set, = 1), or masked (if cleared, = 0).

27 EMULI Emulator (Lower Priority) Interrupt. When the processor is servicing

another interrupt, this bit indicates if the EMULI interrupt is unmasked

(if set, = 1), or masked (if cleared, = 0). An EMULI occurs on reset and

when an external device asserts the EMU

pin. This interrupt has a lower

priority than EMUI, but higher priority than software interrupts.

28 SFT0I User Software Interrupt 0. When the processor is servicing another

interrupt, this bit indicates if the SFT0I interrupt is unmasked

(if set, = 1), or masked (if cleared, = 0). An SFT0I occurs when a pro-

gram sets (= 1) this bit.

29 SFT1I User Software Interrupt 1. When the processor is servicing another

interrupt, this bit indicates if the SFT1I interrupt is unmasked

(if set, = 1), or masked (if cleared, = 0).

30 SFT2I User Software Interrupt 2. When the processor is servicing another

interrupt, this bit indicates if the SFT2I interrupt is unmasked

(if set, = 1), or masked (if cleared, = 0).

31 SFT3I User Software Interrupt 3. When the processor is servicing another

interrupt, this bit indicates if the SFT3I interrupt is unmasked

(if set, = 1), or masked (if cleared, = 0).

Table B-7. IMASKP Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...