ADSP-21368 SHARC Processor Hardware Reference 3-83

External Port

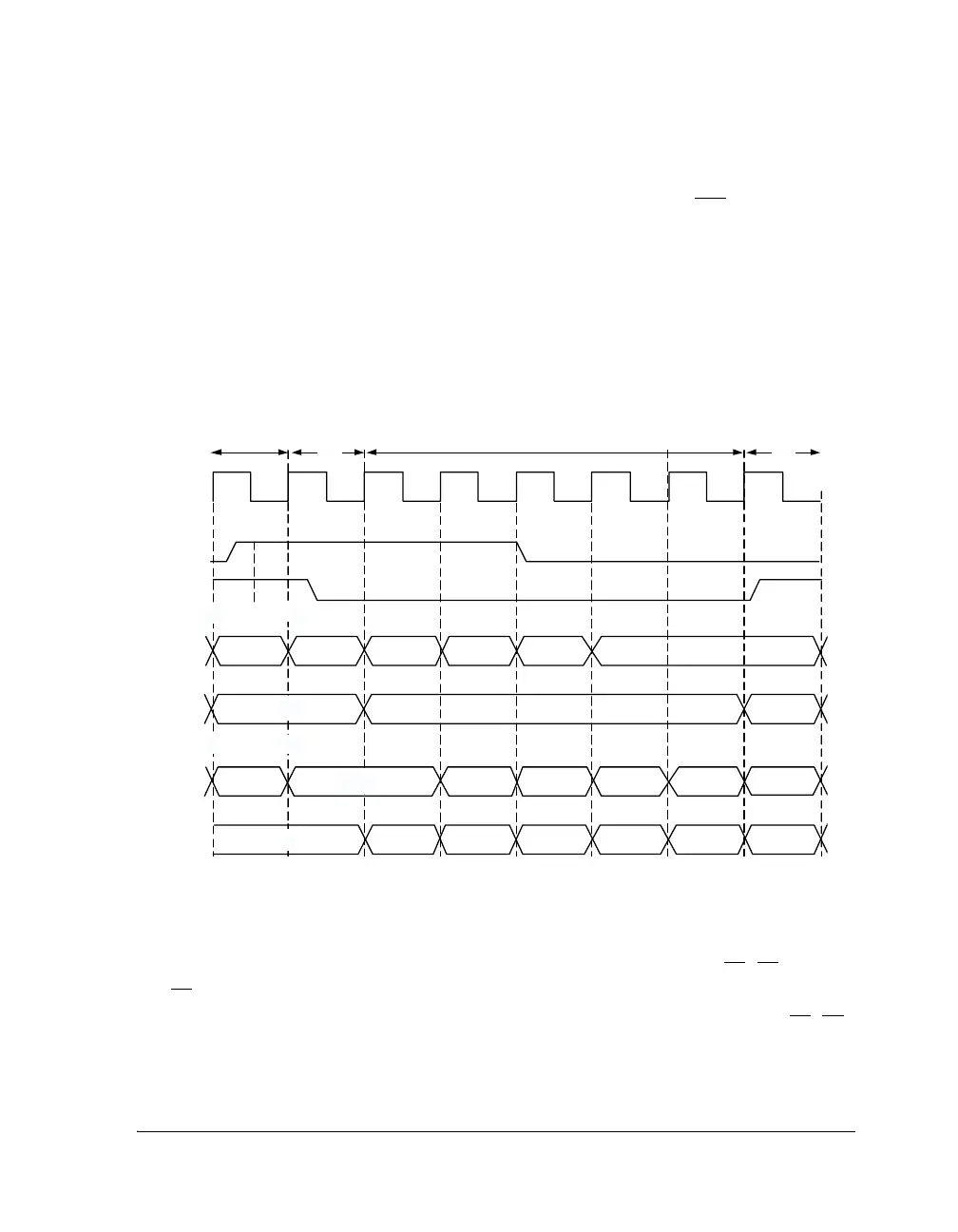

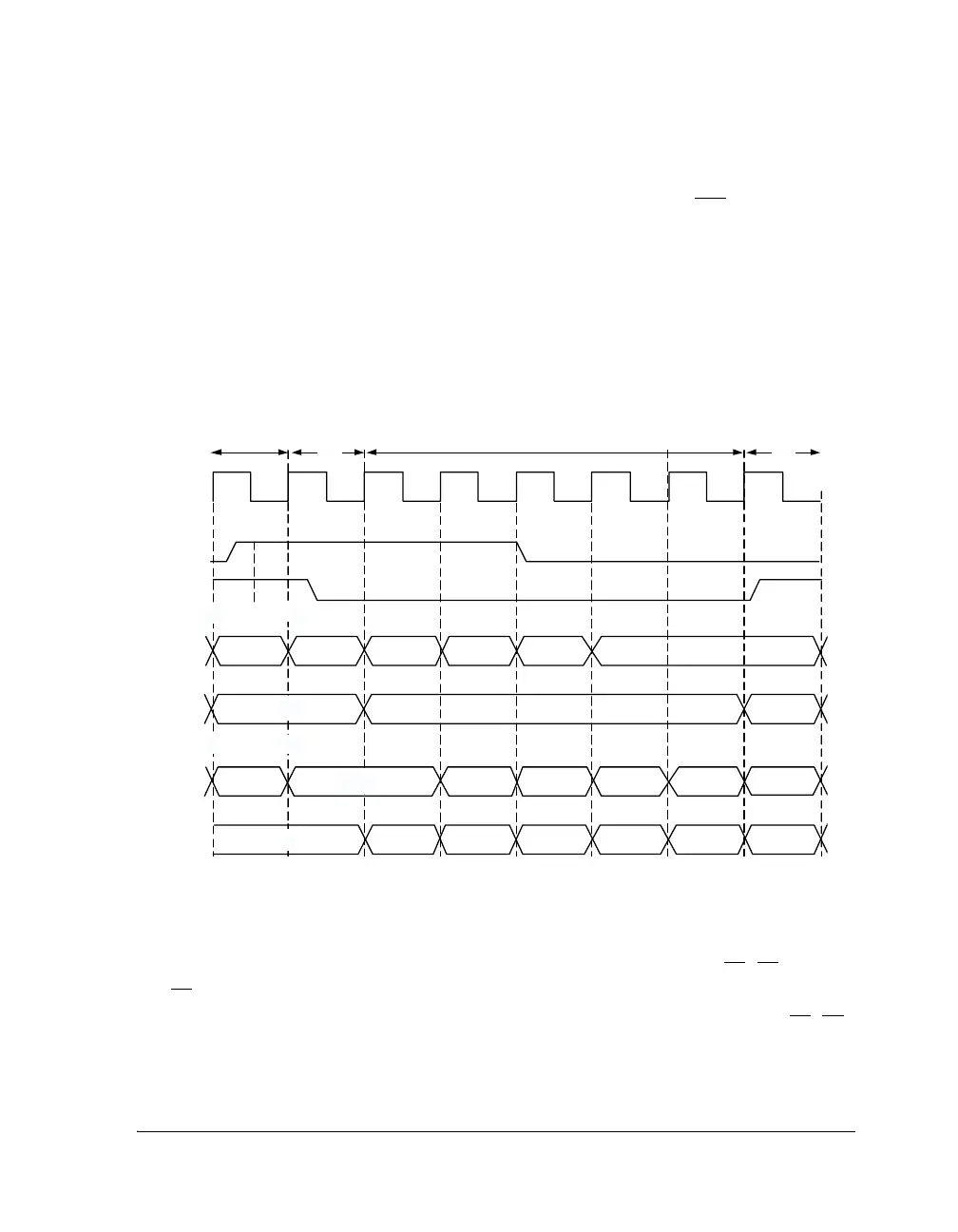

After conditions determine that a bus transition cycle is going to occur,

every processor in the system evaluates the priority of the

BRx lines asserted

within that cycle. For a description of bus arbitration priority, see “Bus

Arbitration Priority (RPBA)” on page 3-86. The processor with the high-

est priority request becomes the bus master on the following cycle, and all

of the processors update their internal records to indicate which processor

is the current bus master. Figure 3-15 shows typical timing for bus

arbitration.

The actual transfer of bus mastership is accomplished by the current bus

master three-stating the external bus—DATA31-0, ADDR23-0, RD, WR, and

MS3-0—at the end of the bus transition cycle and the new bus master driv-

ing these signals at the beginning of the next cycle. The bus strobes RD, WR,

Figure 3-15. Bus Arbitration Timing

INTERNAL

OPERATION

INTERNAL

OPERATIO N

INTERNAL

OPERATION

INTERNAL

OPERATION

INTERNAL

OPERATION

EXTERNAL

ACCESS

UNDRIVEN

PERFORM

ACCESS

INTERNAL

OPERATION

EXTERNAL

ACCESS

INTERNAL

OPERATION

EXTERNAL

ACC ESS

INTERNAL

OPERATION

INTERNAL

OPERAT ION

UNDRIVEN

HO LD SIGNA L

STABLE

PERFORM

ACC ESS

HO LD SIGNA L

STABLE

PERFOR M

ACCESS

PERFORM

ACCESS

BRX SAMPLED

AT THIS POINT

BUS REQUESTS

CLK IN

BR1

BR2

EXECUTE

FLOW

BUS

ACTIVE

EXECUTE

FLOW

BUS

ACTIVE

PROCESSOR #1

IS BUS MASTER

PROCESSOR #2

IS BUS MASTER

BTC

BTC

EXTERNAL

ACCESS

HOLD S IGNA L

STABLE

UNDRIVEN

PROCESSOR WITH ID=1

PROCESSOR WI TH ID=2

Loading...

Loading...