ADSP-21368 SHARC Processor Hardware Reference 4-53

Digital Audio/Digital Peripheral Interfaces

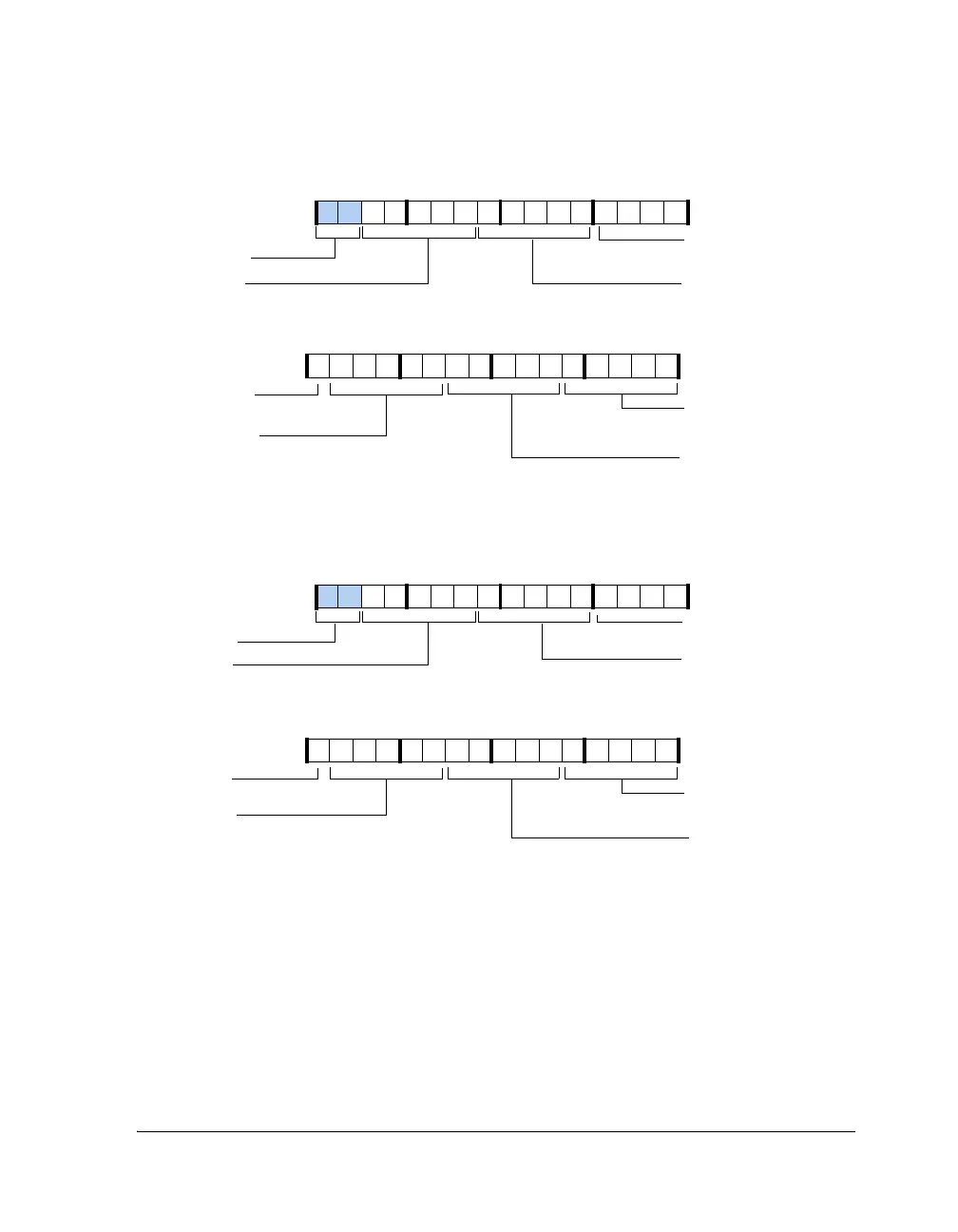

Figure 4-42. SRU2_INPUT1 Register

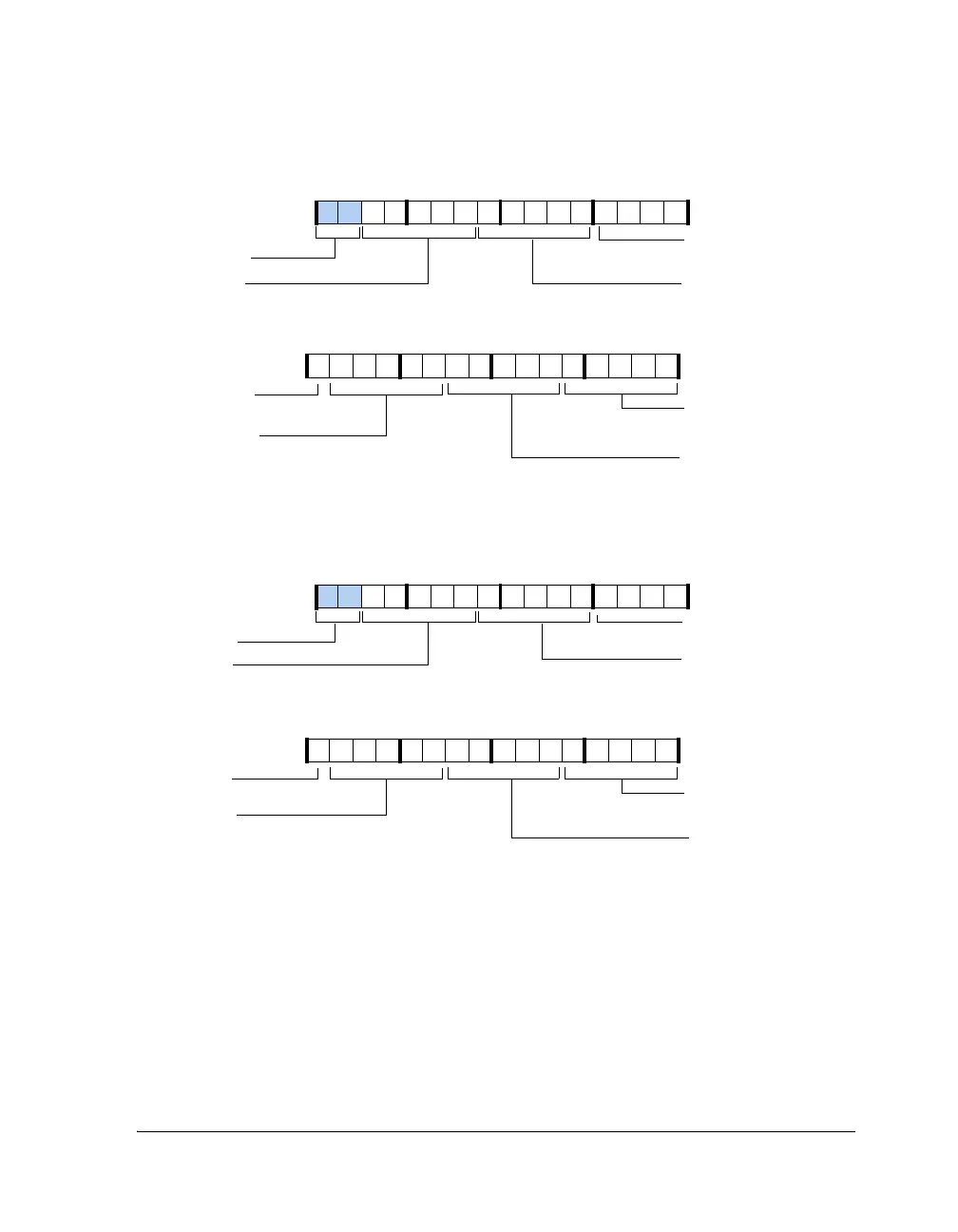

Figure 4-43. SRU2_INPUT2 Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000110101100000

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0001011000000000

TWI_SCLK_I

TWI Serial Clock Input

UART1_RX_I

UART 1 Receiver Input

TWI_SDATA_I

TWI Serial Data Input

UART0_RX_I

UART 0 Receiver Input

SPIB_CLK_I

SPI B Clock Input

SPIB_DS_I

SPIB Device Select Input

SRU2_INPUT1

(0x1C01)

UART1_RX_I

UART 1 Receiver Input

Reset = 0x1AC02C00

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0000000000000000

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

FLAG6_I

Flag 6 Input

FLAG4_I

Flag 4 Input

FLAG5_I

Flag 5 Input

TIMER2_I

Timer 2 Input

TIMER1_I

Timer 1 Input

TIMER0_I

Timer 0 Input

SRU2_INPUT2

(0x1C02)

FLAG4_I

Flag 4 Input

Reset = 0x00000000

Loading...

Loading...