ADSP-21368 SHARC Processor Hardware Reference 5-53

Serial Ports

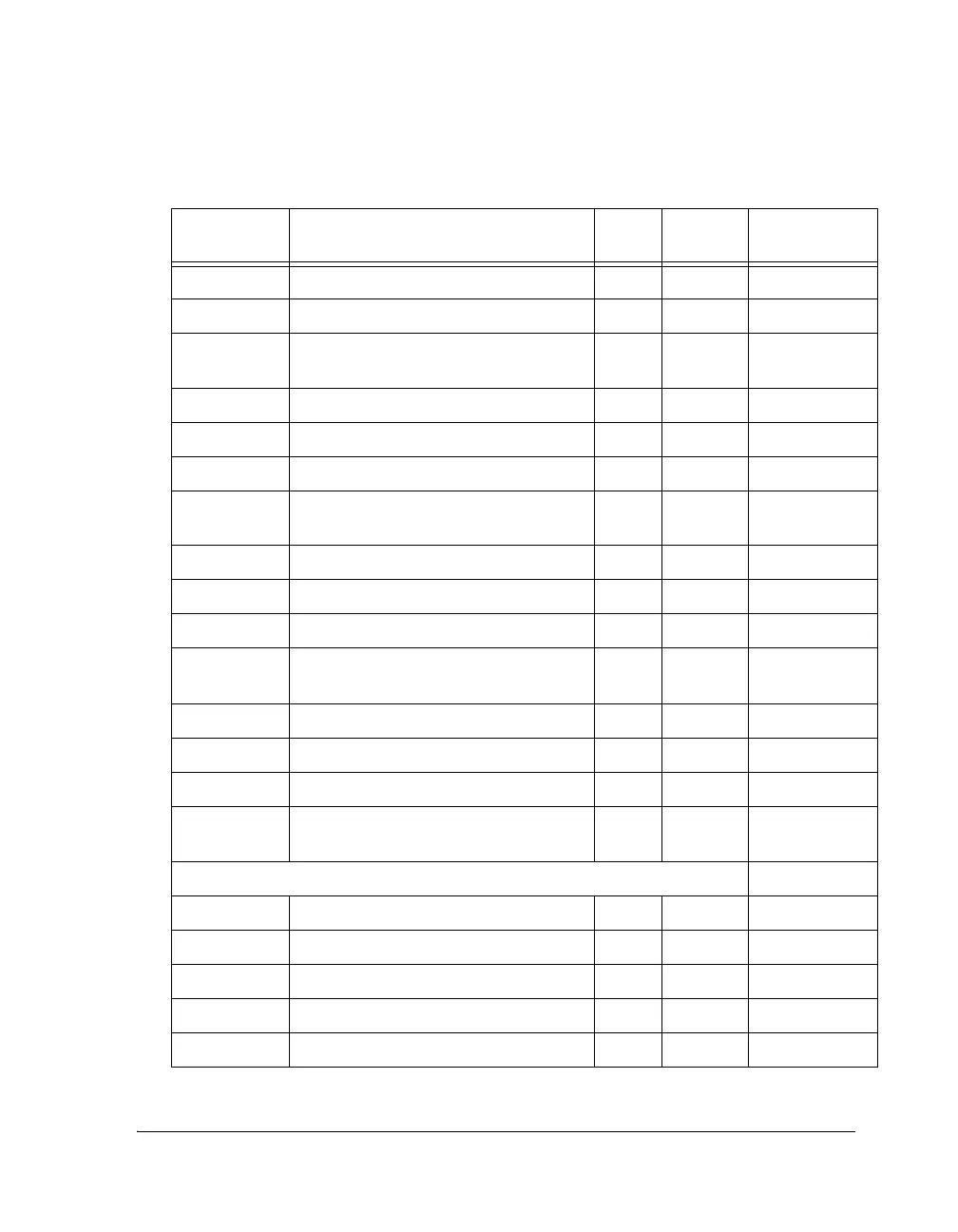

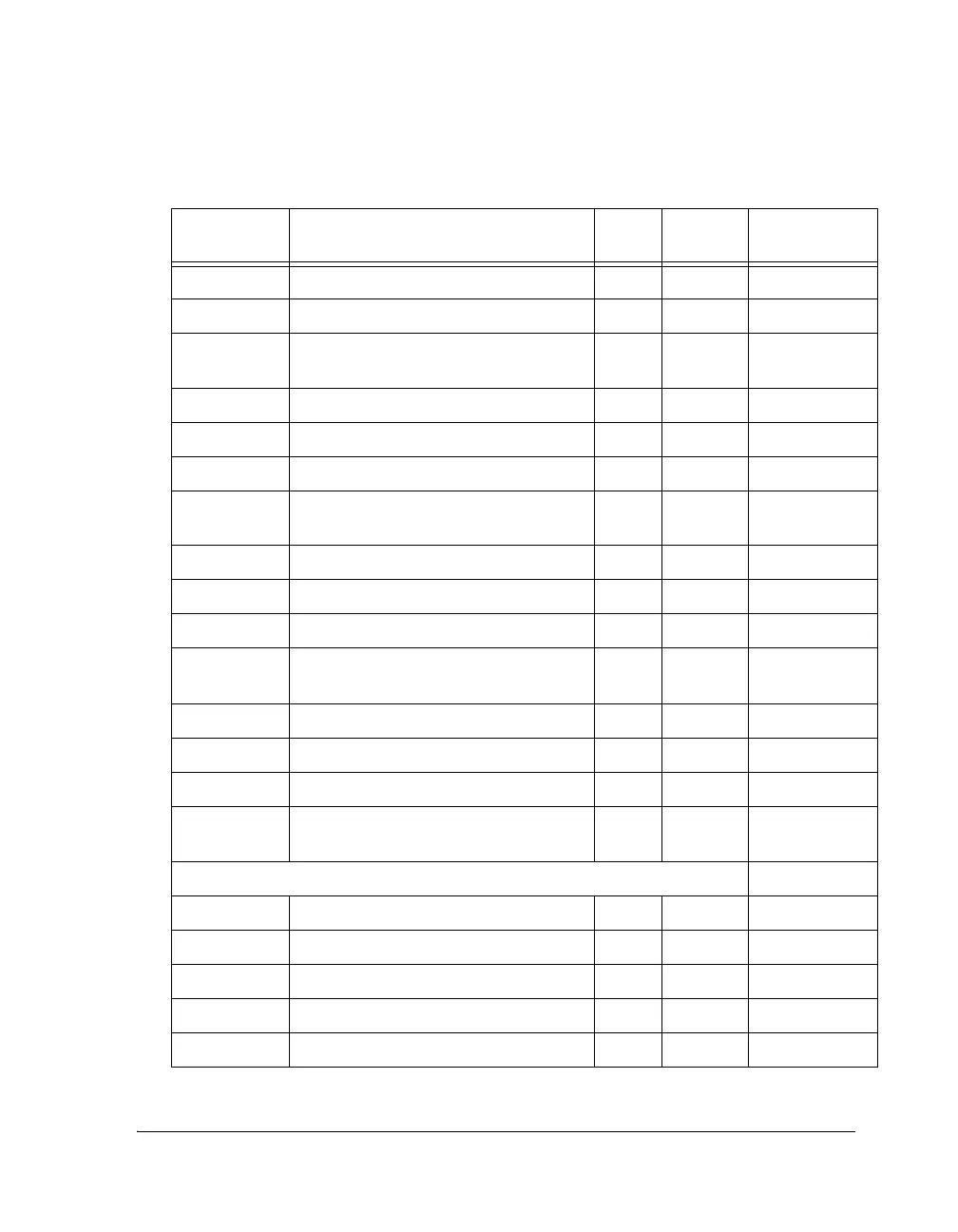

IM2A Internal Modifier for DMA Channel 2A 16 1 00441

C2A Counter for DMA Channel 2A 16 1 00442

CP2A Chain Pointer for DMA Chaining

Channel 2A

20 1 00443

II2B Address for DMA Channel 2B 19 1 00444

IM2B Internal Modifier for DMA Channel 2B 16 1 00445

C2B Counter for DMA Channel 2B 16 1 00446

CP2B Chain Pointer for DMA Chaining

Channel 2B

20 1 00447

II3A Address for DMA Channel 3A 19 1 00448

IM3A Internal Modifier for DMA Channel 3A 16 1 00449

C3A Counter for DMA Channel 3A 16 1 0044A

CP3A Chain Pointer for DMA Chaining

Channel 3A

20 1 0044B

II3B Address for DMA Channel 3B 19 1 0044C

IM3B Internal Modifier for DMA Channel 3B 16 1 0044D

C3B Counter for DMA Channel 3B 16 1 0044E

CP3B Chain Pointer for DMA Chaining

Channel 3B

20 1 0044F

Reserved 00450–0045F

TX2A Transmitter FIFO Register in SP2A 32 1 00460

RX2A Receiver FIFO Register in SP2A 32 1 00461

TX2B Transmitter FIFO Register in SP2B 32 1 00462

RX2B Receiver FIFO Register in SP2B 32 1 00463

TX3A Transmitter FIFO Register in SP3A 32 1 00464

Table 5-6. SPORT2 and SPORT3 Registers (Cont’d)

Register

Name

Function Width No. of

Registers

Memory Map

[17:0]

Loading...

Loading...