ADSP-21368 SHARC Processor Hardware Reference 8-11

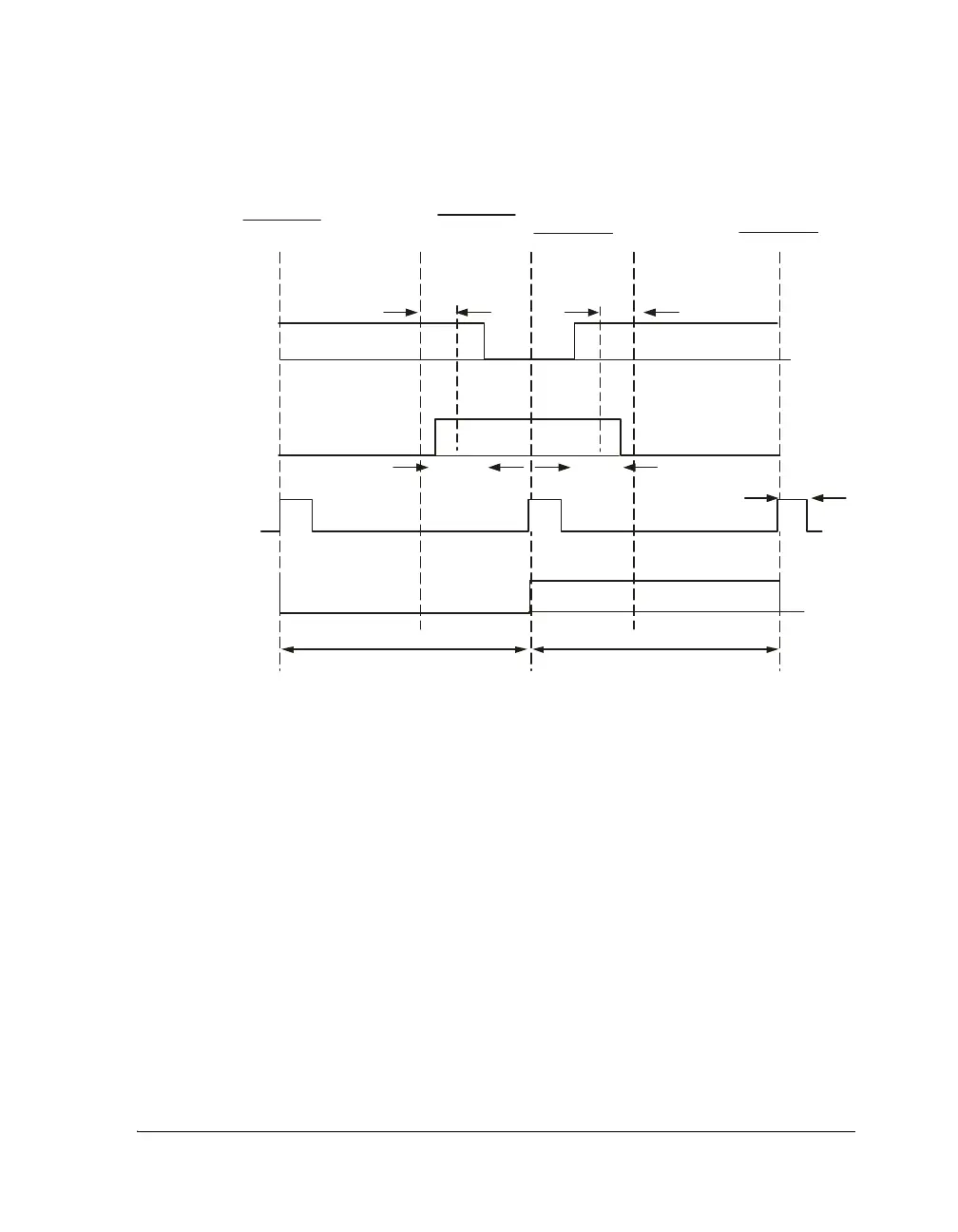

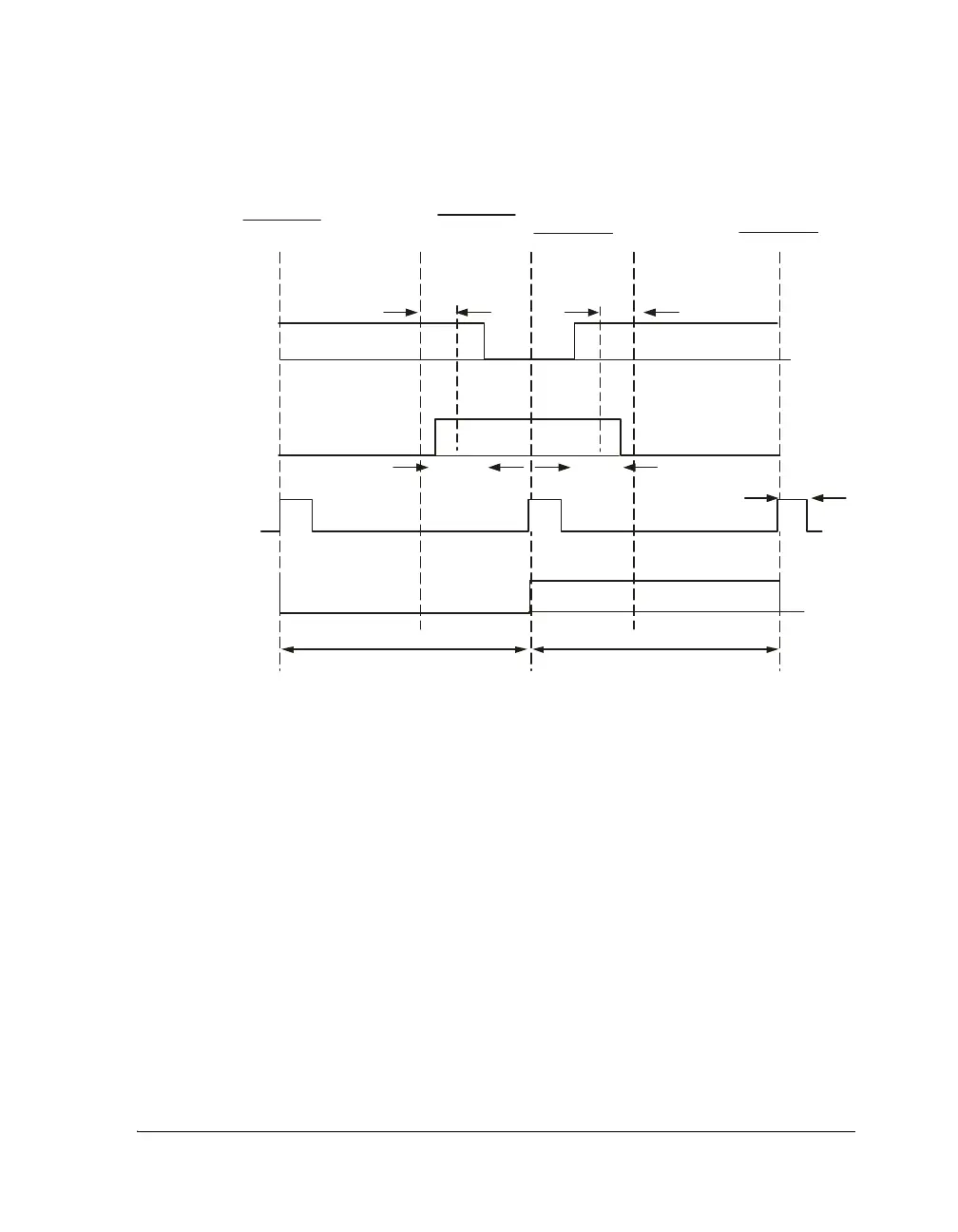

Pulse Width Modulation

Figure 8-3. Center-Aligned Paired PWM in Double-Update Mode,

Low Polarity

......................

.....

......................

.....

PWMCHA

1

PWMCHA

2

PWMPERIOD

1

2

+

00

2xPWMDT

1

2xPWMDT

2

PWMSYNCWT

2

+1

count

pwm_ah

pwm_al

PWMPHASE

pwm_pwmsync_out

PWMSYNCWT

1

+1

PWMPERIOD

1

2

PWMPERIOD

2

2

PWMPERIOD

2

2

_

+

PWMPERIOD

2

PWMPERIOD

1

T

AH

PWMPERIOD

1

2

-----------------------------------------

PWMPERIOD

2

2

-----------------------------------------

PWMCHA

1

PWMCHA

2

PWMDT

1

PWMDT

2

––+++

⎝ ⎠

⎛ ⎞

t

PCLK

×=

T

A

L

PWMPERIOD

1

2

-----------------------------------------

PWMPERIOD

2

2

-----------------------------------------

PWMCHA

1

– PWMCHA

2

– PWMDT

1

PWMDT

2

––+

⎝ ⎠

⎛ ⎞

t

PCLK

×=

Loading...

Loading...