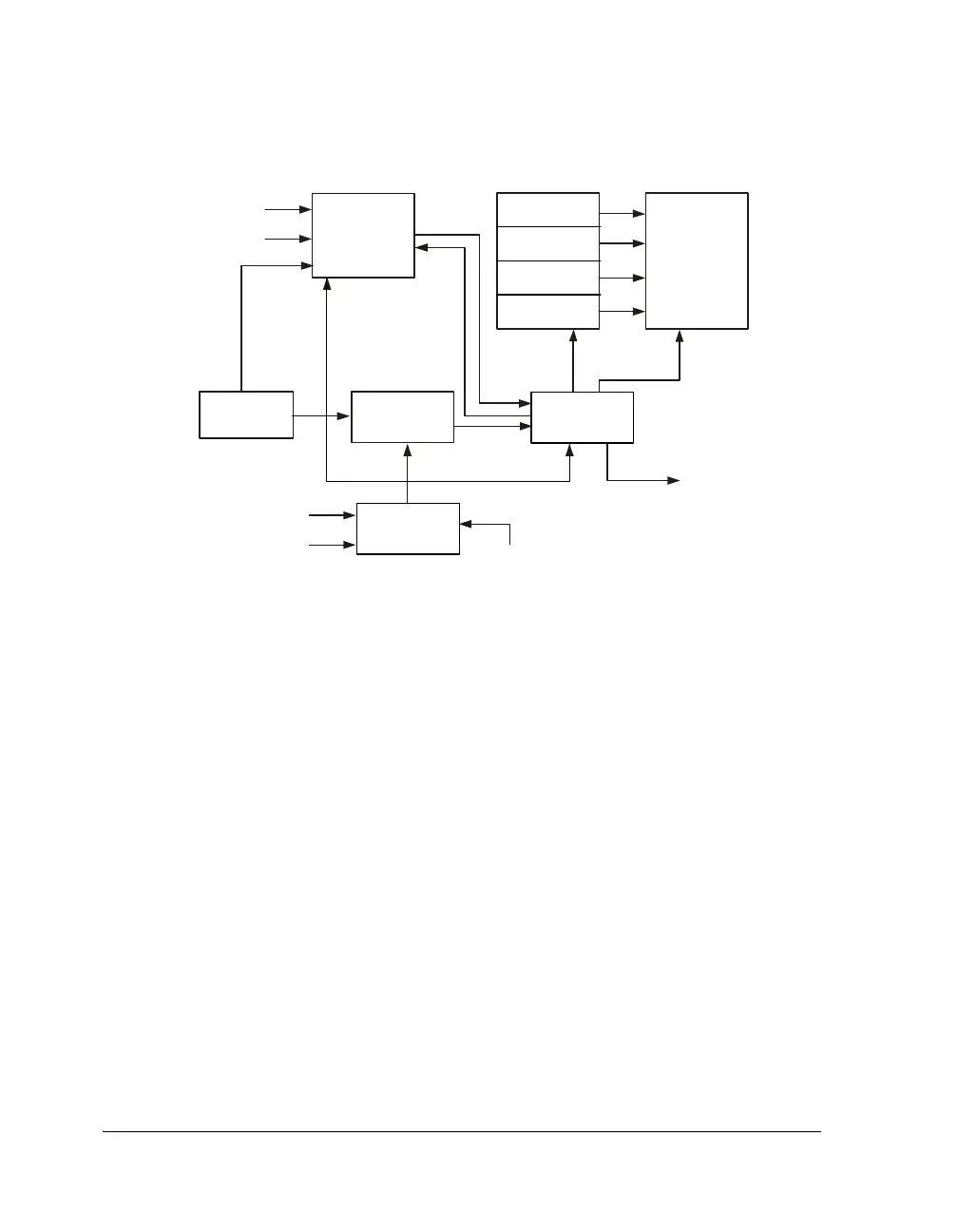

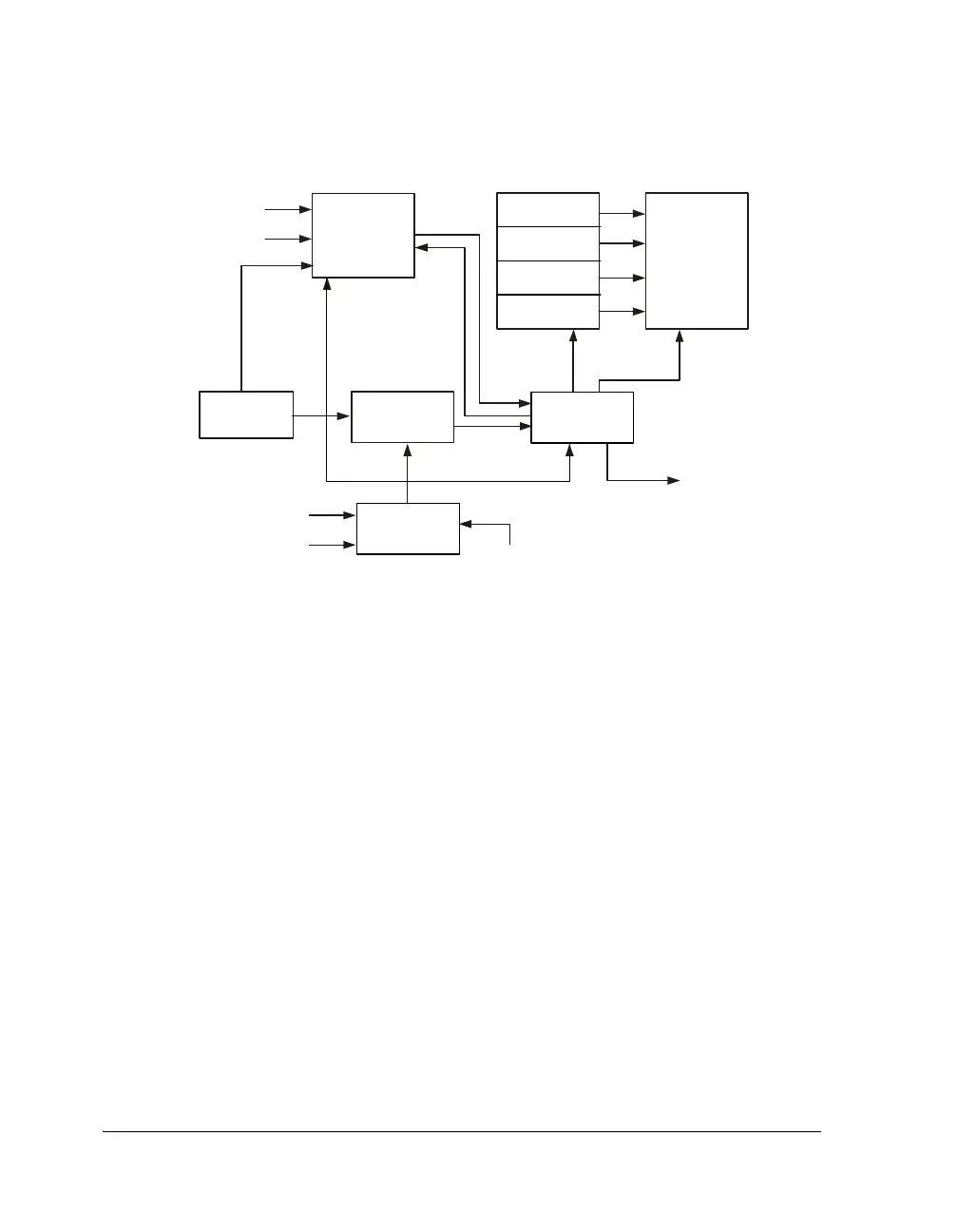

Sample Rate Converter Architecture

10-10 ADSP-21368 SHARC Processor Hardware Reference

low. Increasing the offset of the write address pointer is useful for applica-

tions when small changes in the sample rate ratio between f

S_IN

and

f

S_OUT

are expected. The maximum decimation rate can be calculated

from the RAM word depth and GRPDLYS as (512 – 16)/64 taps = 7.75 for

short group delay and (512 – 64)/64 taps = 7 for long group delay.

The digital-servo loop is essentially a ramp filter that provides the initial

pointer to the address in RAM and ROM for the start of the FIR convolu-

tion. The RAM pointer is the integer output of the ramp filter while the

ROM pointer is the fractional part. The digital-servo loop must be able to

provide excellent rejection of jitter on the f

S_IN

and f

S_OUT

clocks as well

as measure the arrival of the f

S_OUT

clock within 4.97 ps. The digi-

tal-servo loop also divides the fractional part of the ramp output by the

ratio of f

S_IN

/f

S_OUT

for the case when f

S_IN

> f

S_OUT

, to dynamically

alter the ROM coefficients.

Figure 10-5. Sample Rate Converter Architecture

f

S_IN

COUNTER

FIFO

HIGH

ROM A

DIGITAL

SERVO LOOP

FIR FILTER

ROM B

ROM C

ROM D

ORDER

INTERP

SAMPLE RATE

RATIO

SAMPLE RATE RATIO

L/R DATA OUT

EXTERNAL

RATIO

RIGHT DATA IN

LEFT DATA IN

f

S_ IN

f

S_OUT

Loading...

Loading...