SRC Operation

10-14 ADSP-21368 SHARC Processor Hardware Reference

Table 10-3. When the output word width is less than 24 bits, dither is

added to the truncated bits. The right-justified serial data out mode

assumes 64

SCLK_O cycles per frame, divided evenly for left and right.

Please note that 8 bits of each 32-bit subframe are used for transmitting

matched-phase mode data as shown in Figure 10-9 on page 10-18. The

SRC also supports 16-bit, 32-clock packed input and output serial data in

left-justified and I

2

S format.

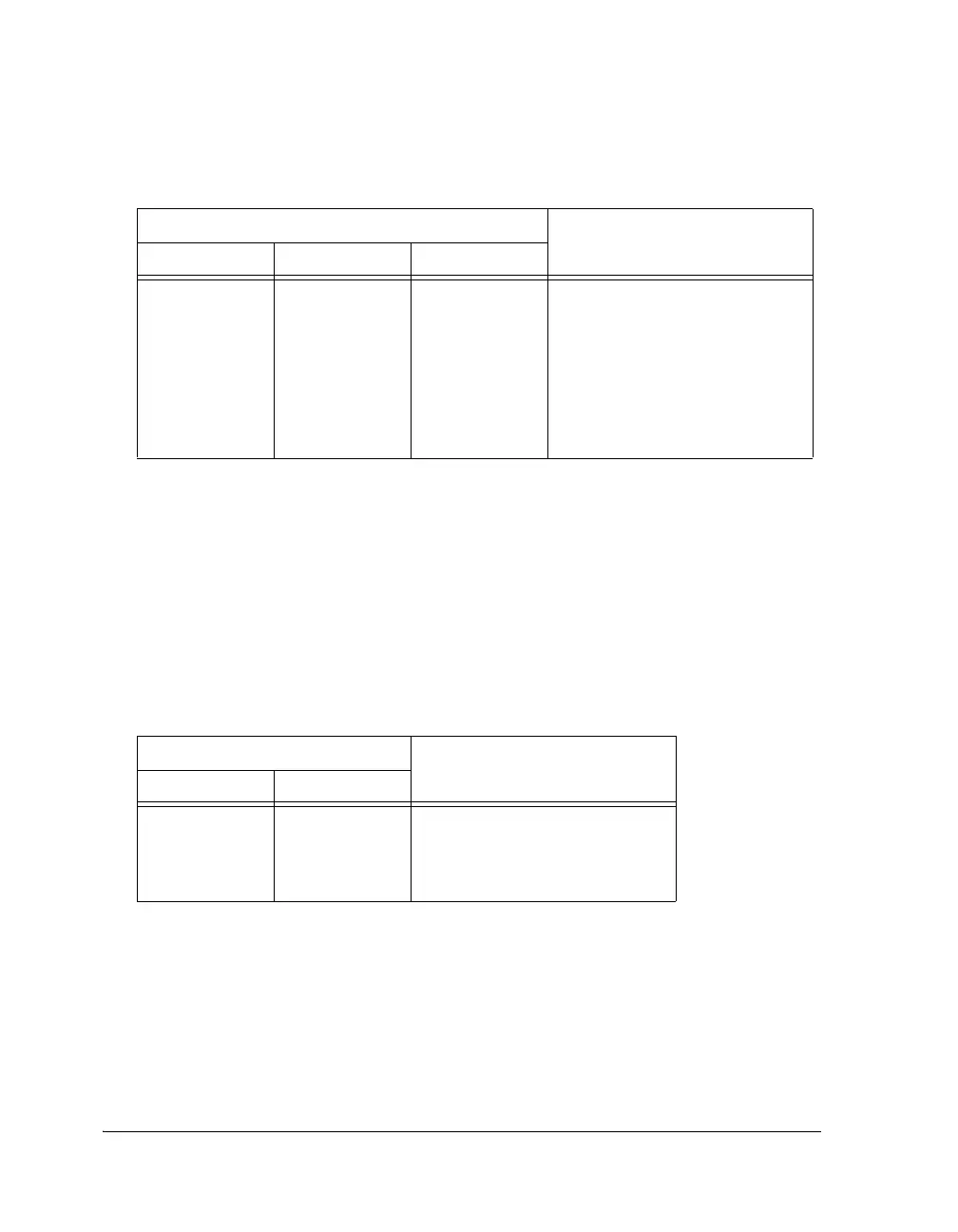

Table 10-1. Serial Data Input Port Mode

SRCx_SMODE_0:2

Interface Format

210

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Left-justified

I

2

S

TDM

RESERVED

Right-justified, 16 bits

Right-justified, 18 bits

Right-justified, 20 bits

Right-justified, 24 bits

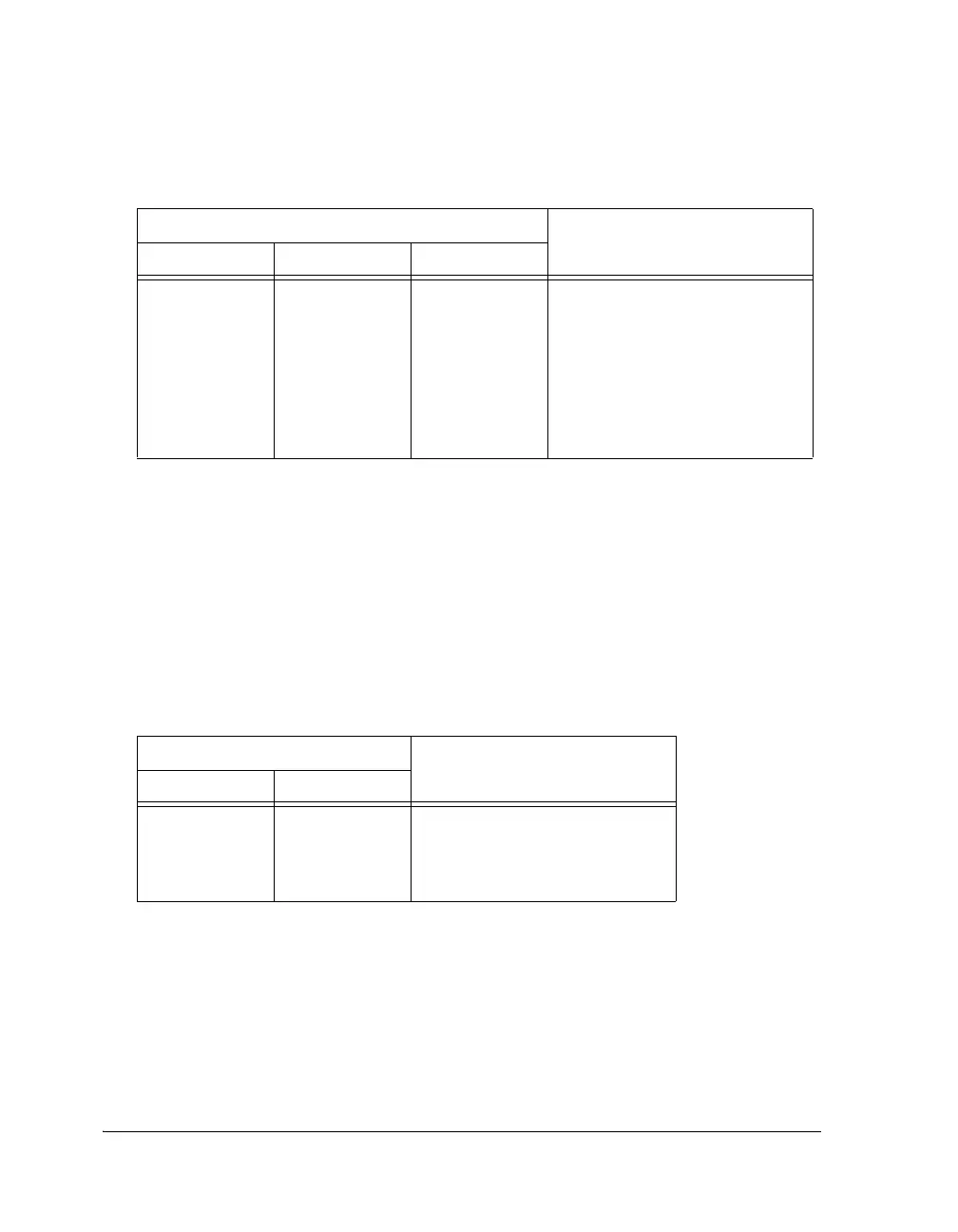

Table 10-2. Serial Data Output Port Mode

SRCx_SMODEOUT_0:1

Interface Format

10

0

0

1

1

0

1

0

1

Left-justified

I

2

S

TDM

Right-justified

Loading...

Loading...