Core Access to IOP Registers

2-4 ADSP-21368 SHARC Processor Hardware Reference

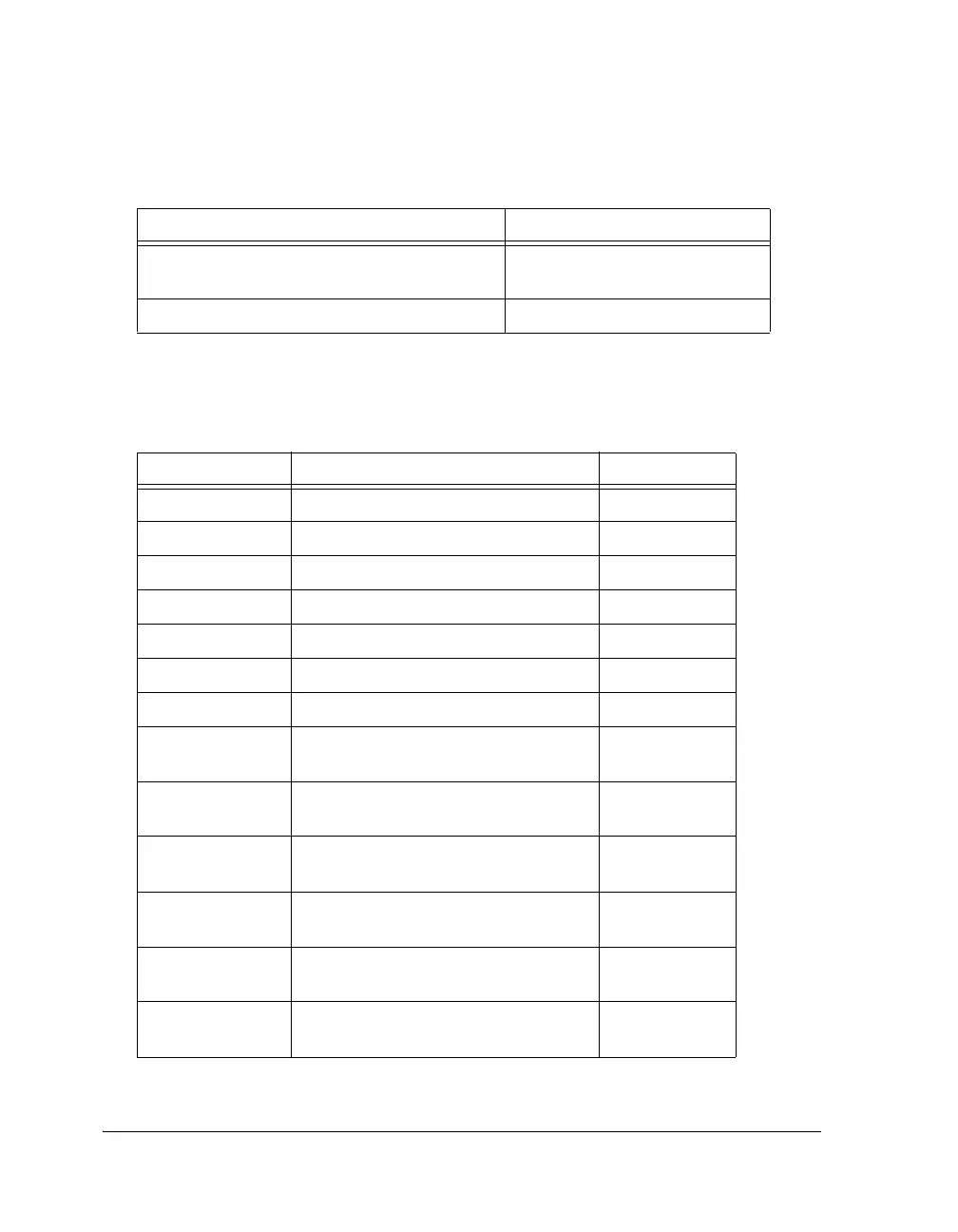

Aborted conditional I/O processor register

read/write

2

3

Conditional I/O processor register read/write

2

9/10

1 Applies to memory-mapped registers from Table 2-2.

2 Applies to all other memory-mapped registers not in Table 2-2.

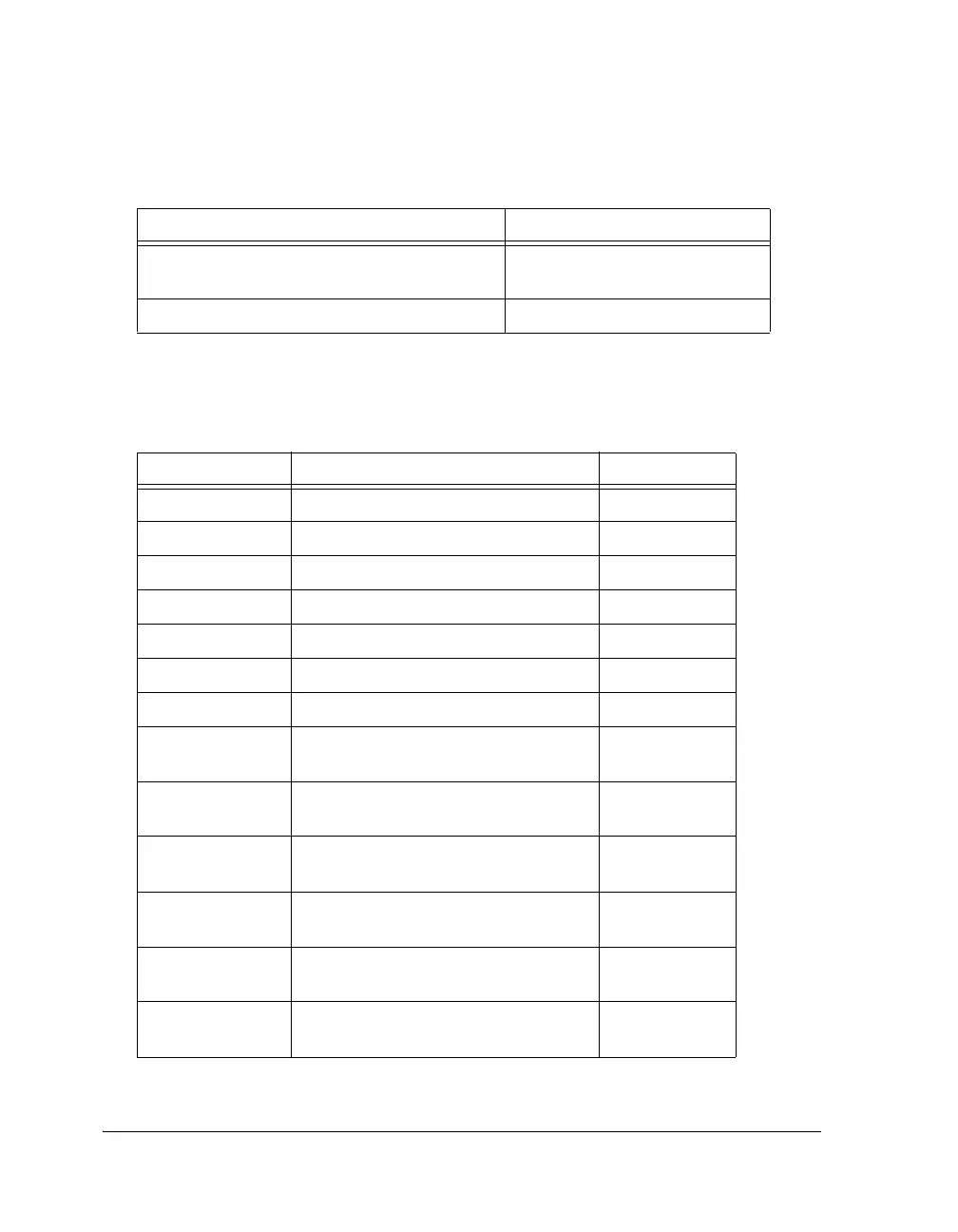

Table 2-2. Memory-Mapped Emulation/Breakpoint Registers

Register Description Address

EEMUIN Emulator input FIFO 0x30020

EEMUSTAT Enhanced emulation status 0x30021

EEMUOUT Emulator output FIFO 0x30022

OSPID Operating system process ID 0x30023

SYSCTL System control 0x30024

BRKCTL Breakpoint control 0x30025

REVPID Emulation/revision ID 0x30026

PSA1S/E Instruction breakpoint address number 1

start/end

0x300A0/

0x300A1

PSA2S/E Instruction breakpoint address number 2

start/end

0x300A2/

0x300A3

PSA3S/E Instruction breakpoint address number 3

start/end

0x300A4/

0x300A5

PSA4S/E Instruction breakpoint address number 4

start/end

0x300A6/

0x300A7

EMUN Number of breakpoints before EMU

interrupt

0x300AE

IOAS/E I/O address breakpoint start/end 0x300B0/

0x300B1

Table 2-1. I/O Processor Stall Conditions (Cont’d)

Type Of Access Number of Core Cycles

Loading...

Loading...