Serial Port Registers

A-32 ADSP-21368 SHARC Processor Hardware Reference

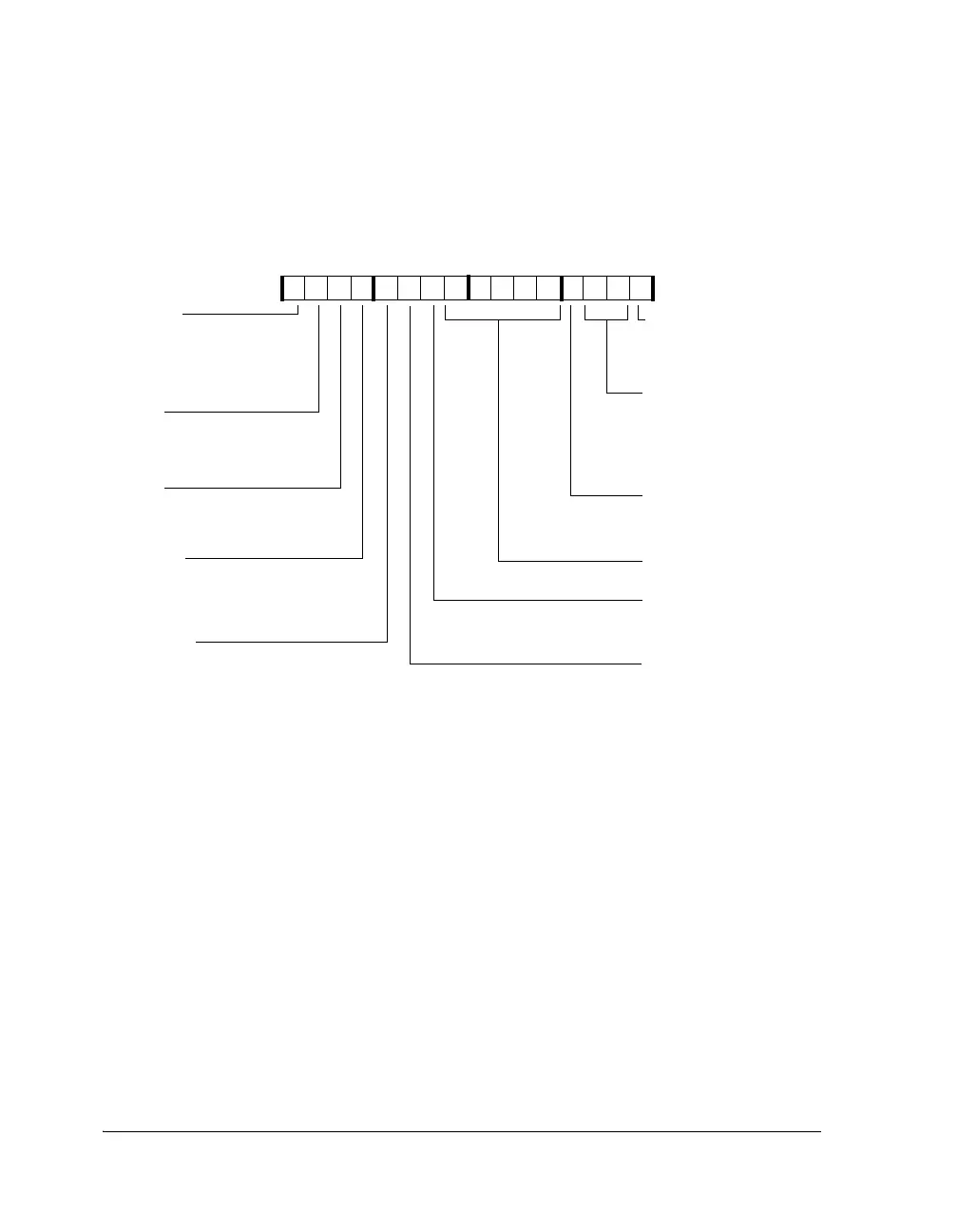

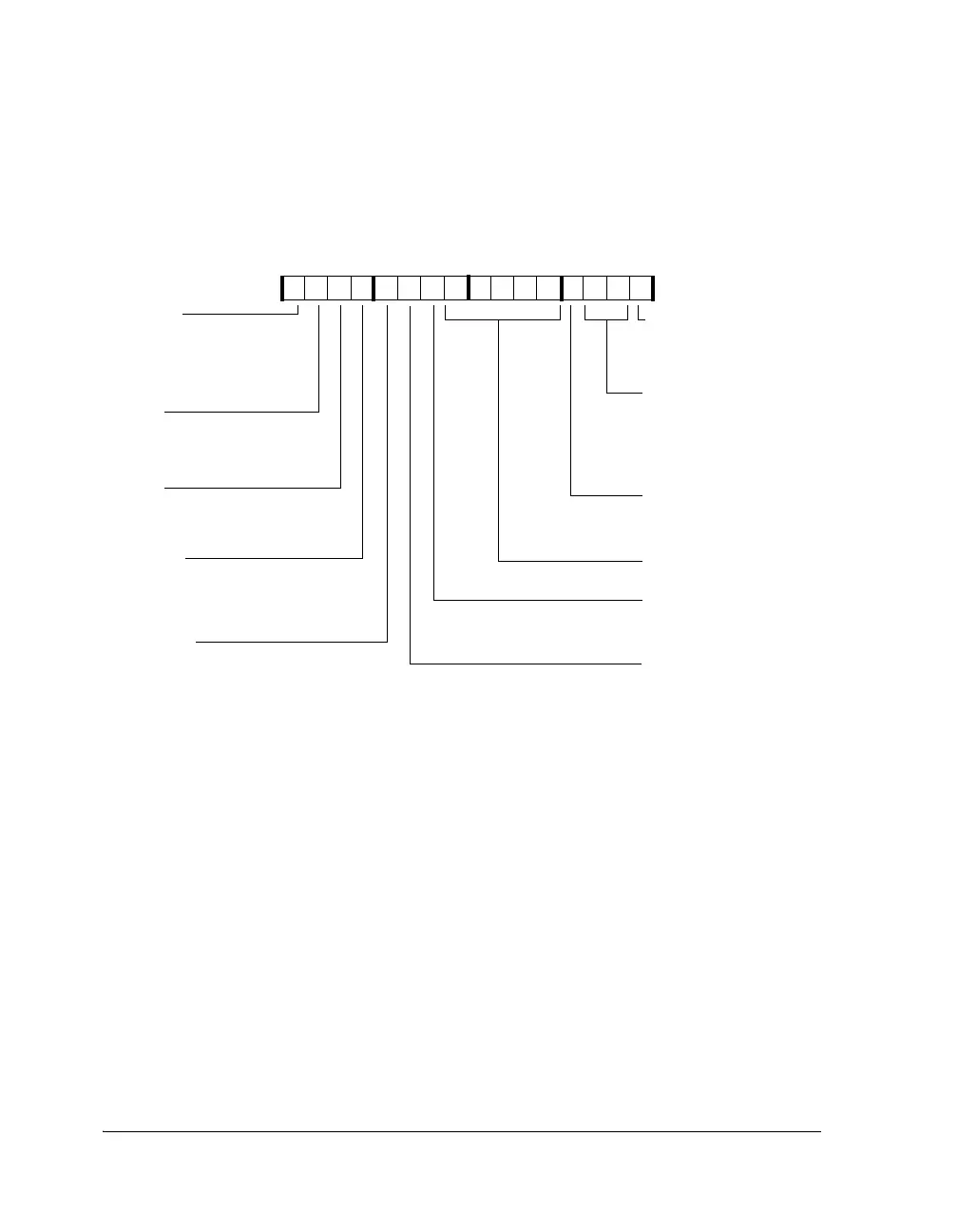

Figure A-14. SPCTLx Register (Bits 0–15) for Standard DSP Serial Mode

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0000000000000000

SPEN_A

DIFS

Data Independent TX FS

(if SPTRAN=1) or RX FS (if

SPTRAN=0)

1=Data independent

0=Data dependent

IFS

Internally-Generated FS

1=Internal

0=External

FSR

Frame Sync Requirement

1=Frame sync required

0=Frame sync not required

CKRE

Clock Edge for Data Frame Sync

Sampling or Driving

1=Rising edge

0=Falling edge

OP MODE

SPORT Operation Mode

0=DSP serial mode/multichannel mode,

this bit must be set to 0

DTYPE

Data Type

00=Right-justify

01=Right-justify, sign extend MS

10=Compand mu-law

11=Compand A-law

ICLK

Internally-Generated

SPORTx_CLK

1=Internal clock

0=External clock

SPORT Enable A

1=Enable

0=Disable

LSBF

Least Significant Bit Format

1=LSB first

0=MSB first

SLEN

Serial Word Length=1

PACK

16/32 Packing

1=Packing

0=No packing

SPCTL0 (0xC00) SPCTL1 (0xC01)

SPCTL2 (0x400) SPCTL3 (0x401)

SPCTL4 (0x800) SPCTL5 (0x801)

SPCTL6 (0x4800) SPCTL7 (0x4801)

Loading...

Loading...